# One step a-Si:H TFT'S with PECVD $SiO_xN_y$ gate insulator

K.F. Albertin and I. Pereyra LME, EPUSP, University of São Paulo, CEP 5424-970, CP61548, São Paulo, SP, Brazil.

Recibido el 27 de octubre de 2004; aceptado el 26 de mayo de 2005

Amorphous silicon thin film transistors (TFT's), utilizing silicon dioxide (SiO<sub>2</sub>), silicon oxynitride (SiO<sub>x</sub>N<sub>y</sub>) and silicon nitride (Si<sub>3</sub>N<sub>4</sub>) obtained by PECVD as gate insulating material, are fabricated through just one masking process and characterized by drain current vs drain voltage and by drain current vs gate voltage ( $I_{ds}$  vs.  $V_{ds}$  and  $I_{ds}$  vs.  $V_{gs}$ ) measurements.

Keywords: One mask step; silicon oxynitride; thin film transistors.

Son fabricados con apenas una etapa de fotolitografía transistores de capa fina de silicio amorfo utilizando, como material dieléctrico de compuerta, dióxido de silicio (SiO<sub>2</sub>), oxinitruro de silicio (SiO<sub>x</sub>N<sub>y</sub>) y nitruro de silicio (Si<sub>3</sub>N<sub>4</sub>) crecidos por PECVD. Los dispositivos son caracterizados por medio de mediciones de corriente de dreno vs voltaje de dreno y corriente de dreno vs voltaje de compuerta ( $I_{ds}$  vs.  $V_{ds}$  y  $I_{ds}$  vs.  $V_{qs}$ )

Descriptores: fotolitográfica; oxinitruro de silicio; transistores de capa fina

PACS: 72.80.Sk; 73.40 Qv

## 1. Introduction

Thin Film Transistors (TFT) with amorphous silicon nitride gate dielectric ( $SiN_x$ ) and amorphous silicon (a-Si:H) active layer are emerging as the most utilized switching device for active matrix liquid crystal displays (AMLCD's) [1–5]. However, low channel field effect mobility and charge trapping in the a-Si:H/SiN<sub>x</sub> interface are described as the major challenges for the improvement of the TFT electrical characteristics [6]. So studies are oriented to alternative dielectrics, among them silicon dioxide (SiO<sub>2</sub>), which in spite of its good insulating properties can not be utilized as a single layer due to its high interface state density with a-Si:H. Some authors utilize an  $N_2$  or an  $NH_3$  plasma treatment of the  $SiO_2$  layer to incorporate nitrogen at the a-Si:H/SiO<sub>2</sub> interface [7]. Also some works have reported the use of  $SiO_xN_y$  in TFT's as double insulating gate  $(SiN_x/SiO_xN_y)$  [8]. In previous [9] works we studied the characteristics of MOS capacitors utilizing  $SiO_xN_y$  dielectric layer, with nitrogen concentration varying from SiO<sub>2</sub> to Si<sub>3</sub>N<sub>4</sub>, and we identified the composition, which leads to the best interface properties. In this work we fabricate and characterize amorphous TFT's with three different dielectric layers ( $SiO_2$ ,  $SiO_xN_y$  and  $Si_3N_4$ ), intending to identify the dielectric film that presents the best insulating/a-Si:H interface properties.

## 2. Experiment

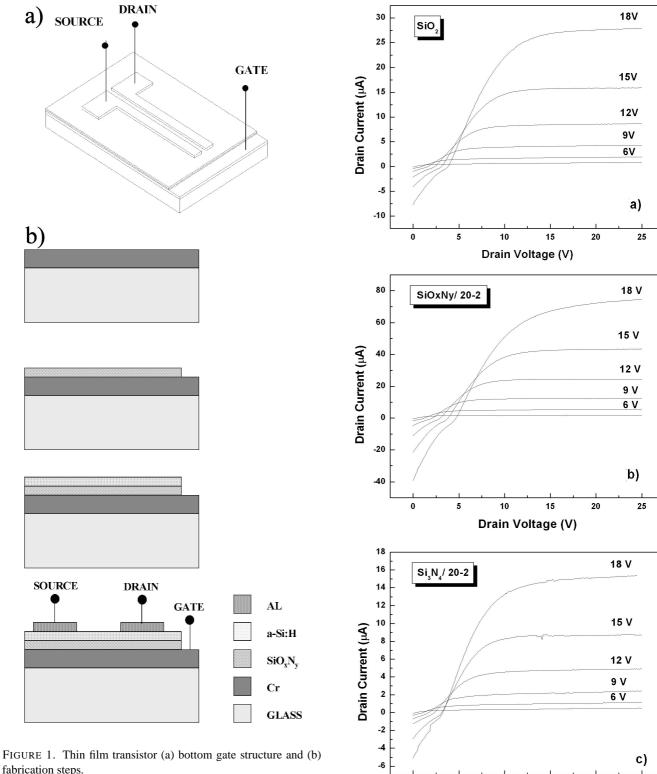

The bottom gate, just one masking step TFT's fabrication process is schematized in Fig. 1.

The devices were fabricated on corning glass, utilizing a chromium electrode as gate contact (300 nm),  $\mathrm{SiO}_x\mathrm{N}_y$  (90 nm),  $\mathrm{SiO}_2$  (70 nm) and  $\mathrm{Si}_3\mathrm{N}_4$  (70 nm,  $\sim 31$  N at %) as insulating layer, undoped a-Si:H active layer (100nm) and aluminum drain and source contacts (300 nm). Both the insulating layer and the active layer were deposited by the PECVD

TABLE I. Deposition conditions for dielectric layers and the active layer of the TFT's.

| Film                             | SiH4<br>(sccm) |    |    | Pressure<br>(mTorr) | Temperature (°C) | Power<br>(Watts) |

|----------------------------------|----------------|----|----|---------------------|------------------|------------------|

| $SiO_2$                          | 3              | 39 | _  | 17                  | 320              | 100              |

| $\mathrm{SiO}_{x}\mathrm{N}_{y}$ | 3              | 3  | 36 | 17                  | 320              | 100              |

| $Si_3N_4$                        | 3              | _  | 39 | 17                  | 320              | 100              |

| a-Si:H                           | 10             | _  | _  | 400                 | 250              | 10               |

technique; the deposition conditions for all the utilized films are shown in Table I.

The thickness of the a-Si:H and  $SiO_xN_y$  films was measured in an Alpha Step 500 Tencor surface profiler. The drain current vs drain voltage ( $I_{ds}$  vs  $V_{ds}$ ) and the drain current vs gate voltage ( $I_{ds}$  vs  $V_{gs}$ ) characteristic curves for these devices were obtained in an HP 4145B Parameter Analyzer.

#### 3. Results

In Fig. 2 the typical output characteristics for transistors with a channel width W of 2 mm and a channel length L of 20  $\mu$ m, with SiO<sub>2</sub>, SiO<sub>x</sub>N<sub>y</sub> and Si<sub>3</sub>N<sub>4</sub>, gate dielectric layer, respectively are shown.

It is observed that the drain current values vary with the gate voltage applied, and a well-defined saturation region is observed for all the devices and geometries. In this way the transconductance is well defined. It is observed that the TFT with  $\mathrm{SiO}_x\mathrm{N}_y$  gate dielectric presents the highest drain current. It is also observed that the drain current is different from zero for zero drain voltage, indicating that these devices present a leakage current ( $\mathrm{I}_g$ ), probably due to pinholes in the dielectric layer.

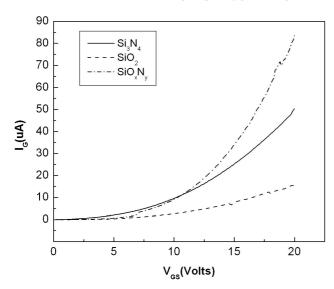

In Fig. 3 the gate current vs gate voltage  $(I_{gx}V_{gs})$  characteristics for the three insulating layers are shown; the highest

fabrication steps.

$I_G$  value obtained was for the TFT with  $SiO_xN_y$  gate dielectric. Thus for an appropriate parameter extraction, the  $I_{ds}$ values should be corrected for leakage current. Also the parasitic drain and source series resistance may have a considerable effect on the current - voltage transistor characteristics for a-Si:H TFT's [10].

FIGURE 2. Thin Film Transistor characteristic curve ( $I_{ds}$  vs.  $V_{gs}$ ) for W=2 mm and  $L=20~\mu{\rm m}$  a) SiO<sub>2</sub>, b) SiO<sub>x</sub>N<sub>y</sub>, c) Si<sub>3</sub>N<sub>4</sub>.

Drain Voltage (V)

25

The series resistance is associated with the amorphous silicon film thickness and with the contact resistance, and it af-

FIGURE 3. Gate current vs gate voltage for  $SiO_2$ ,  $SiO_xN_y$ , and  $Si_3N_4$  insulator layer TFT's.

fects the extraction of the channel mobility and increases the threshold voltage value [11]. The amorphous silicon thickness contribution to  $R_s$  was estimated from the amorphous silicon resistivity ( $\sim 6.2 \times 10^4~\Omega$  cm), leading to a value of  $2.3 \times 10^3~\Omega$ , which means that for the highest  $I_{ds}$  value obtained it will give a voltage loss of 0.1V, thus having a negligible effect on the  $I_{ds}$  vs.  $V_{ds}$  characteristics. Regarding to the contact resistance contribution, the non-linear behavior of  $I_{ds}$  for small  $V_{ds}$  suggests that the Al/a-Si:H contacts are in fact rectifying Schottky barriers; n+ source and drain regions would be necessary in order to guarantee good ohmic contacts. In this way, the  $V_{ds}$  loss in these contacts is difficult to compute, thus preventing series resistance correction. Consequently, the extracted mobility values are underestimated and the threshold voltage ones are overestimated.

The threshold voltage  $(V_{th})$  values were obtained by the extrapolation of the square root of the drain saturation current as a function of the gate voltage; the values obtained were 4.6 V, 3.8 V and 2.2 V for,  $SiO_2$ ,  $SiO_xN_y$  and  $Si_3N_4$  and gate insulator TFT's respectively. These values are compatible with those reported in the literature for standard bottom gate TFT (between 2-4 V) [10]. Finally we extracted the channel mobility in saturation ( $\mu$ ) regime, using the saturation drain current expression  $\{I_{ds(lin)} = \beta^*[(V_g - V_{th})^*V_{ds} - V_{ds}^2/2]\},$ where  $\beta = (W/L)C_{ox}\mu$ , and Cox is the dielectric capacitance. We found a channel mobility of 0.05, 0.3 and 0.03 cm $^2/(V s)$ for TFT's using  $SiO_2$ ,  $SiO_xN_y$  and  $Si_3N_4$  respectively. The highest value was obtained for the SiOxNy gate dielectric TFT, which probably is correlated with better insulator/a-Si:H interface properties, which at a time can be related with the lower mechanical stress associated with this film, as observed in previous works [12].

#### 4. Conclusions

Bottom gate amorphous silicon hydrogenated based TFT's, with silicon dioxide  $SiO_2$ ,  $SiO_xN_y$  and  $Si_3N_4$  insulating layer and undoped amorphous silicon active layer were fabricated through a one deposition and one masking step process. A well-defined transistor action was obtained for all devices. We found the highest mobility for the silicon oxynitride gate insulator TFT, a result which can be related to the lower mechanical stress associated with this film leading to better insulator/a-Si:H interface properties.

## Acknowledgments

The authors are grateful to Dr. Marco I.A. Cháves for his helpful discussion of the results. This work was financially supported by FAPESP (Process No 00/10027-3 and 03/02837-3) and CNPq.

<sup>1.</sup> K. Yue, J. Eletrochem. Soc. 142 (1995) 2486.

<sup>2.</sup> M.J. Powell, IEEE Trans. Elect. Dev. 12 (1989) 2753.

<sup>3.</sup> R.E.I. Schropp, B. Stannowski, and J.K. Rath, *J. of Non-Cryst. Sol.* **299-302** (2002) 1304.

B. Stannowski, J.K Rath, and R.E.I Schropp, *Thin Solid Films* 430 (2003) 220.

W. Sigurd, G. Helena, C. I-Chun, and W. Ming, *Thin Solid Film* 430 (2003) 15.

<sup>6.</sup> G. Lavareda et al., Thin Solid Films 427 (2003) 71.

S.K. Kim, K.S. Lee, J.H. Kim, C.H. Hong, and J. Jang, Solid-State Phenomena 44 (1995) 973.

<sup>8.</sup> K Hiranaka and T. Yamagughi, *Jap. Journal of App. Phys.* **29** (1990) 229.

K.F Albertin, I. Pereira, and M.I. Alayo, Materials Characterization 5568 (2003) 149.

<sup>10.</sup> K Lee, M. Shur, T. Fjeldly, and T.Ytterdal, *Semiconductor Device Modeling for VLSI* Prentice Hall, (New Jersey 1993) 509.

<sup>11.</sup> C.Ying and J. Kanick, Solid-State Electronics 42 (1998) 705.

M.I. Alayo, D. Criado, L.C.D. Gonçalves, and I.Pereyra, *Journal of Non-Cryst. Solids* 338-340 (2004) 76.