1. Introducción

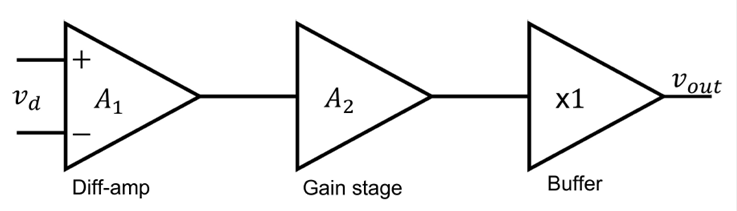

El desarrollo de circuitos Integrados (CIs) con tecnologías manométricas es un reto para todo diseñador. Es así porque cada día hay una demanda adicional en el desempeño de los circuitos y sistemas de las nuevas aplicaciones, sean para su inclusión en el desarrollo de circuitos para la exploración espacial, en los nuevos procesadores, en el desarrollo de sensores inteligentes, en dispositivos portátiles, para ser parte de las Tecnologías de la Información (TI) y/o el Internet de las Cosas (IC), por citar algunas [1-3]. Aún más, el diseño de circuitos analógicos se vuelve una tarea multi-objetivo por las nuevas tendencias que apuestan a la reducción en los voltajes de alimentación sin degradar la eficiencia de los sistemas, con mayores frecuencias de operación, con reducido consumo de potencia y del área de integración y operación en un amplio rango de temperatura, entre otros. En el diseño analógico, su objetivo es mapear las restricciones de acondicionamiento de señales en bloques de circuitos electrónicos que cumplan con las especificaciones de las distintas aplicaciones. Un ejemplo puede verse en la Fig. 1, donde se muestra el diagrama a bloques de un amplificador de dos etapas con buffer de salida. La primer etapa es un amplificador diferencial [4] y enseguida una etapa de ganancia que puede ser de mayor ganancia que la primer etapa, y por último un buffer. Si el amplificador es condicionado para manejar cargas capacitivas, el buffer no se requiere. Pero, si es condicionado para manejar cargas resistivas o cargas RC, se utiliza un buffer [5].

El diseño en sí es una actividad desafiante porque el proceso de diseño se enfoca en especificaciones como el rango dinámico, ruido, ganancia, fase y ancho de banda, por mencionar algunas. Estos y más parámetros están estrechamente relacionados con el tamaño del transistor y también con la tecnología CMOS de manufactura. La mayoría de las veces, el proceso de diseño impone compensaciones de diseño, y algunas se basan en la experiencia del diseñador y en la tecnología que se usa [6].

En la práctica, el circuito más demandante en su diseño es el amplificador CMOS tanto de transconductancia como de voltaje (OTA y OpAmp por sus siglas en inglés, respectivamente), o lo que es lo mismo, su diseño es a la medida de las especificaciones impuestas por la aplicación particular. El amplificador CMOS es un bloque fundamental en el diseño de circuitos analógicos, muy utilizado en circuitos electrónicos como los convertidores analógico-digital (ADC por sus siglas en inglés), filtros activos RC o switched capacitor, circuitos sample and hold e instrumentación, entre otros [7-10].

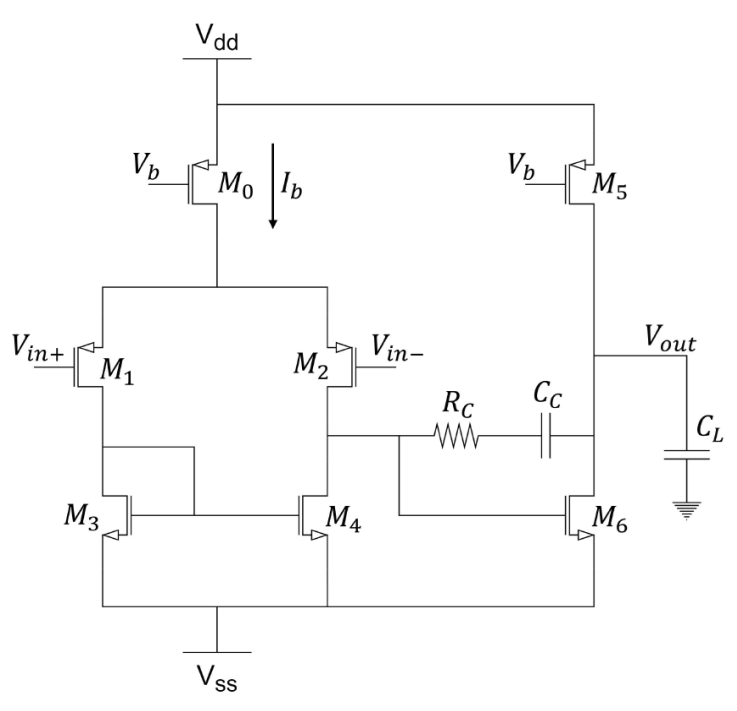

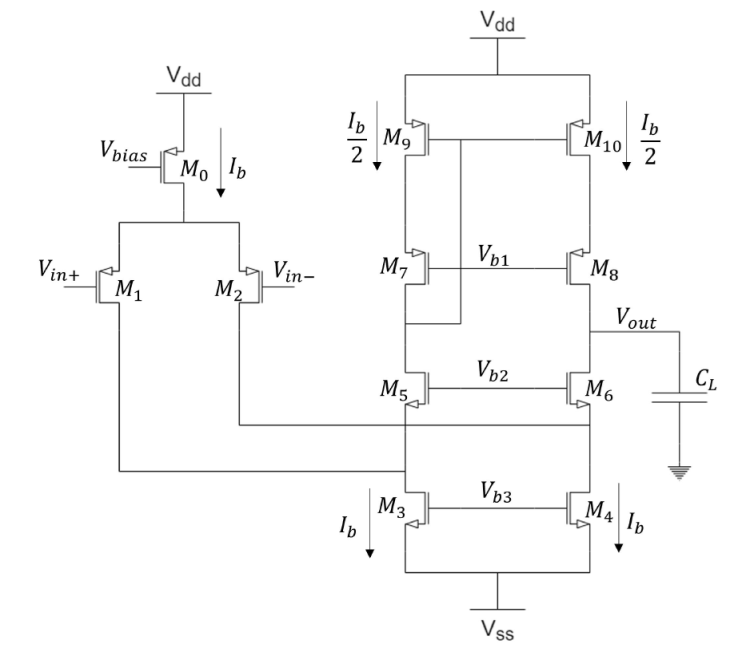

Dos arquitecturas de amplificadores CMOS son el amplificador de dos etapas con compensación Miller y el amplificador folded cascode (FC), mostrados en las Fig. 2 y 3, respectivamente. Su popularidad viene del buen balance entre ganancia, fase y ancho de banda [4,5]. En la práctica existen diversas topologías que se han reportado para diferentes aplicaciones, tanto para el amplificador Miller [11-15], como para el amplificador FC [16-20], donde explican por qué unas son eficientes en uno o varios parámetros de desempeño, pero ni una sola se diseña para ser de propósito general. Aunado a esto, uno de los principales retos para el diseño del OTA u Op-amp es la metodología de diseño, que la mayoría de los casos se realiza con un análisis a “mano” para obtener modelos analíticos que se usan como ecuaciones de diseño, comúnmente basadas en un comportamiento LEVEL = 1 de Spice, el cual puede considerarse un comportamiento ideal [4,21]. Aún más, debido a que se manejan esas ecuaciones de diseño, el método no considera aquellos efectos no-ideales de la tecnología utilizada, llevando a redimensionar el circuito con procedimientos prueba-y-error para alcanzar las especificaciones de diseño. En contraposición, para disminuir estas limitaciones está la metodología gm/ID, que se basa en la curva de eficiencia de esa relación (obtenidas del comportamiento del transistor para cualquier tecnología) y obtener los parámetros de diseño requeridos para una aplicación en particular. En el estado del arte se encuentran dos arquitecturas muy interesantes: el amplificador de dos etapas con compensación feedforward (CFF) [22], y el amplificador recycling folded cascode (RFC) [16]. Estas son variaciones a las arquitecturas Miller y FC, respectivamente. Debido a lo anterior, este trabajo se centra en el análisis, diseño, implementación, simulación y comparación de cuatro amplificadores CMOS con salida simple. Aunque la salida completamente diferencial tiene ventajas como la inmunidad al ruido, amplio output swing y mayor ganancia, hay aplicaciones donde se utiliza la salida simple [23-25,4], por lo tanto en este trabajo se elige el diseño con salida simple para mostrar un análisis práctico y cómo proceder con el diseño. Lo anterior con el interés de diferenciar las ventajas y desventajas de cada amplificador, y que son diseñados con las reglas de diseño de una tecnología CMOS 130 nm. También se muestra una serie de pasos generales para el diseño, utilizando la metodología g m /I D , la cual considera la relación de la transconductancia g m , y la corriente del transistor I D , junto con la corriente de drenaje normalizada I D /(W/L) como parámetros fundamentales para explorar el espacio de diseño.

Este artículo está estructurado de la siguiente manera. En la Sec. 2 se describe el principio básico de operación del amplificador Miller. Se muestra también el resultado del análisis de pequeña señal, así como varios parámetros que describen su desempeño y que están disponibles en la literatura [4,5,11-15,21]. La Sec. 3, por otro lado, describe las ventajas de la metodología gm/ID así como su alcance práctico. A manera de ejemplo se definen parámetros específicos de desempeño (que han de satisfacer los amplificadores bajo diseño) con el propósito de mostrar cómo con la metodología se determina el dimensionamiento de cada transistor. En la Sec. 4, se muestra el diseño de un amplificador FC, donde además se describe cómo usando los recursos del simulador, se cuantifican otros parámetros de desempeño como ICMR y CMRR (del inglés Input Common Mode Range y Common Mode Rejection Ratio, respectivamente); todo ello a temperatura ambiente. En la Sec. 5 se muestra el diseño de un amplificador RFC y se incluye el impacto de las variaciones de las fuentes de alimentación en la respuesta del amplificador. Otro propósito es mostrar que el simulador permite graficar funciones analíticas basadas en curvas de desempeño específicas de los circuitos bajo diseño. Para terminar con el diseño de amplificadores, en la Sec. 6, se muestra el amplificador de dos etapas con compensación feedforward. Posterior a esto se realiza la comparación de resultados en la Sec. 7. Allí mismo se incluye un ejemplo de aplicación donde se muestra el efecto de los parámetros fundamentales (g m y r o ) del OTA en el desempeño de una red de filtrado activo RC pasa-bajas cuya frecuencia de corte f c debe ser 1 MHz. De la misma manera se muestra un filtro pasa-bajas con ganancia unitaria, cuya f c está determinada por la carga capacitiva. El fin último es mostrar que el desempeño esperado no está definido sólo por los elementos pasivos (R y C) sino también por el amplificador. Finalmente en la Sec. 8 se presentan las conclusiones.

2. Amplificador Miller

El diseño del amplificador parte del análisis de su arquitectura para definir una estrategia de diseño con base en los parámetros de interés (ganancia, ancho de banda, slew rate, margen de fase, etc). Uno de los análisis más importantes es en pequeña señal, con el cual se definen expresiones en frecuencia que dan una aproximación del comportamiento del sistema y definir los parámetros bajo el control del diseñador. La arquitectura del OTA Miller se muestra en la Fig. 2, donde un par diferencial de entrada PMOS es la primera etapa de amplificación, y la etapa de salida es un amplificador de fuente común. Obsérvese que entre ambas etapas hay una red RC, la cual pudiera no requerirse y ello depende de diversos factores. Por ejemplo, si el amplificador Miller maneja una carga capacitiva C L , es posible que el margen de fase -del amplificador en lazo abierto- no garantice la estabilidad cuando se requiera incluir un lazo de retroalimentación. Entonces, para garantizar la estabilidad, el capacitor de compensación C c ayuda a corregir el margen de fase usando el efecto Miller [4], y cuyo valor depende del valor de la carga C L y del dimensionamiento del amplificador. Nótese que al ser un amplificador de dos etapas, su función de transferencia puede modelarse como un sistema de segundo orden. Ahora bien, el capacitor C c afecta la posición del polo dominante y lo mueve a bajas frecuencias (ese efecto se denomina pole-splitting), mientras que el polo no dominante lo mueve a frecuencias altas. Sin embargo, debido a la inclusión de C c , el cual forma una conexión feedforward, pudiera dar lugar a un cero que afectará el margen de fase y en consecuencia a la estabilidad; en un diagrama de Bode el cero se aprecia entre los polos del sistema. Cuando es el caso el cero puede ser removido al usar un resistor R c de cancelación (del cero) en serie con C c . Pero, muy importante, pole-splitting sí da lugar a un cero, pero no necesariamente aparece entre los polos. No obstante, hay quienes recomiendan el uso de R c para eliminar al cero [5].

2.1. Análisis de pequeña señal

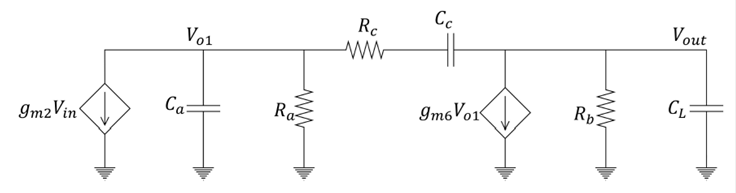

Este análisis se realiza con ayuda del circuito equivalente mostrado en la Fig. 4. La función de transferencia H M (s) y la ganancia en baja frecuencia A DC,0 están dadas por (1) y (2), respectivamente [4,5]:

donde

Figura 4 Circuito equivalente en pequeña señal del amplificador Miller; los transistores operan en saturación y polarizados en fuerte inversión.

Tabla I Definición de elementos del circuito equivalente del amplificador Miller.

| R a = 1/(g ds2 + g ds4 ) |

| R b = 1/(g ds5 + g ds6 ) |

| C a = C db2 + C gd4 + C gs6 |

El primer polo ω s1 definido por la Ec.(3), es el polo dominante y está controlado mayoritariamente por el capacitor de compensación C c , donde vemos que si éste aumenta su valor, ω s1 se desplaza a frecuencias menores. Por el contrario, el segundo polo ω s2 , definido por la Ec. (4), está controlado en mayor porcentaje por el capacitor de carga C L .

Es importante señalar que para el diseño del amplificador Miller, debido al valor de la carga capacitiva (C L = 1 pF) y considerando la relación (9), es conveniente utilizar un resistor de cancelación para propósitos ilustrativos. Si bien es sabido que la implementación de resistores en silicio, tiende a consumir un área mayor de diseño, R c puede ser implementado fácilmente con un transistor NMOS operando en la región lineal [5]. El cero ω z está representado por la Ec. (5), y se observa que se desplaza a frecuencias altas si R c = 1/g m6 .

donde g m6 es la transconductancia del transistor M 6. Por otro lado, el producto ganancia-ancho de banda (GBW), el margen de fase (P M), slew rate (SR) y C c , están determinadas por las Ecs. (6), (7), (8) y (9), respectivamente [4,5]:

donde I b es la corriente de polarización. Estos parámetros, (6)-(9), son de interés porque representan la base de las especificaciones de diseño del amplificador. Es importante señalar que estas expresiones son válidas debido a que (como se comentó) se realizó un análisis para identificar los polos ω s1 y ω s2 , y considerando que este último se sitúa a una frecuencia mayor a la frecuencia de transición ω T , entonces la función H M (s) puede aproximarse a un sistema de primer orden con ω s1 como polo dominante:

válido para todas las frecuencias que satisfacen jsj < ω T , y donde A DC,0 es la ganancia a lazo abierto a muy baja frecuencia. En esta condición, el ancho de banda está definido por la frecuencia ω p1 y es donde la ganancia A DC,0 pierde 3 dB, en consecuencia puede demostrarse que en la aproximación de 1 er orden, la frecuencia de transición, o de 0 dB, se obtiene con el producto de la ganancia y el ancho de banda. A partir de aquí el diseñador debe desarrollar una estrategia de diseño con base en diferentes parámetros para alcanzar los objetivos de diseño. Una estrategia aquí propuesta es usar la metodología g m /I D para realizar el dimensionamiento de los transistores.

3. Metodología g m /I D

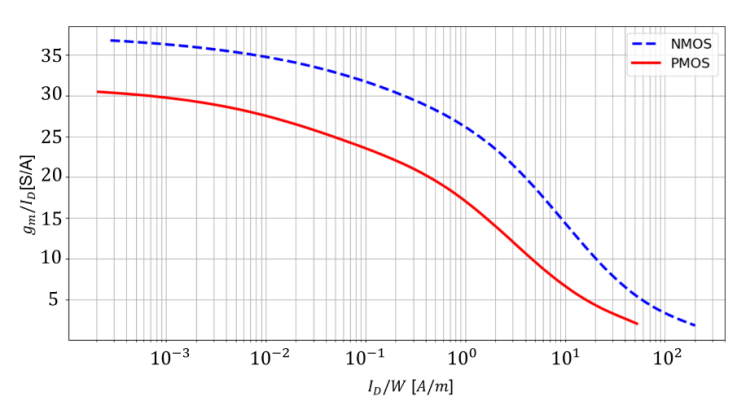

Es una técnica de diseño semi-empírica, sustentada en la información de las curvas de desempeño obtenidas de la simulación eléctrica del transistor MOS, entre las cuales las más importantes son la eficiencia del transistor g m /I D y la densidad de corriente normalizada I D /(W/L), cuya gráfica se puede ver en la Fig. 5 y se obtuvo según se indica en Ref. [26]. Considerando que la relación g m /I D y la corriente normalizada I D /(W/L) son independientes de las dimensiones del transistor Ref. [27], la relación entre éstas es una característica única para todos los transistores del mismo tipo (NMOS o PMOS) en una tecnología especifica. De este modo, la obtención de las curvas características de los transistores NMOS y PMOS se obtienen considerando una longitud de canal L particular (para este trabajo L = 360 nm). La relación g m /I D es un indicador de las regiones de operación (débil, moderada y fuerte inversión), y cada una de éstas presenta características diferentes. Para la región de débil inversión se obtiene una mayor eficiencia de corriente, un rango amplio de voltaje de salida, pero se obtiene una frecuencia ω T baja y transistores con dimensiones grandes. Para fuerte inversión se logra mayor velocidad de operación con ω T grande y dimensiones pequeñas del transistor, pero con una eficiencia pobre de corriente y un bajo rango de voltaje de salida. Una buena relación entre velocidad, ganancia y dimensiones del transistor se encuentra en la región moderada, la cual es una buena opción de operación del transistor. Por lo anterior, es importante señalar que los rangos en las regiones de operación serán diferentes dependiendo de la tecnología CMOS utilizada [26,27]. Para el presente trabajo las curvas mostradas en la Fig. 5 incluye los rangos de las regiones que se muestran en la Tabla II, y son obtenidas usando Cadence para una tecnología CMOS 130 nm.

Tabla II Regiones de operación del transistor MOS.

| Región de operación | Eficiencia de transistor (g m /I D ) |

|---|---|

| Fuerte | < 10 |

| Moderada | 22 > g m /I D > 10 |

| Débil | > 22 |

Esta cualidad de la curva g

m

/I

D

vs I

D

/W puede ser ampliamente usada durante la fase de diseño cuando la razón W/L es desconocida [28]. Esta técnica favorece que el diseñador, una vez determinada la región de operación, dimensione al transistor. Entonces para determinar sus dimensiones físicas, el diseñador sólo requiere conocer la densidad de corriente I

D

/W, la eficiencia del transistor g

m

/I

D

y la co-corriente I

D

que circulará por éste [26,27]. En Ec. (11) se describe la relación entre la corriente

Con ayuda de las curvas mostradas en la Fig. 5, se puede encontrar la I

D

/W correspondiente a la g

m

/I

D

propuesta y/o calculada, y a su vez, ubicar la región de operación del transistor. Con (12), que relaciona la corriente

Es importante señalar que la metodología g m /I D es una ayuda para la aproximación del diseño analógico. Como se mencionó anteriormente, esta metodología permite la interacción de las tres regiones de operación del transistor. Pero, ¿qué pasa con la ley cuadrática que describe al transistor? Sabemos que la ley cuadrática determina el comportamiento en saturación de la corriente de drenaje I D [4]:

donde μ es la movilidad de los portadores de carga, C ox es la capacitancia de óxido, W y L son el ancho y largo del canal del transistor, V GS es el voltaje de compuerta-fuente y V T H es el voltaje de umbral. En Refs. [4,26,27] se determina que la ley cuadrática falla completamente en la región de débil inversión, y en fuerte inversión no es precisa debido a los efectos de canal corto [4,5,29]. Para la operación en inversión moderada no existe un modelo simple que pueda usarse o que describa un comportamiento aproximado. Por lo anterior, una alternativa de modelo simple que proporciona una intuición en el diseño analógico es la ley cuadrática, que puede usarse para entender las tendencias del comportamiento de un circuito, pero no para calcular el dimensionamiento de los transistores. Por esta razón una buena práctica en el diseño analógico, aplicada en este trabajo, es usar el análisis de transistores en saturación, usando su modelo en pequeña señal (como el mostrado en la Fig. 4) para llegar a expresiones que ayuden a comprender el comportamiento aproximado del circuito, y así identificar parámetros que puedan ser de ayuda para alcanzar las especificaciones de diseño como las mostradas en Ecs. (6)-(9).

3.1. Diseño del amplificador Miller con metodología g m /I D

Es de interés mostrar el desempeño de las topologías de amplificadores mostrados en este trabajo, por lo cual en la Tabla III se proponen especificaciones de diseño que servirán como base del uso de la metodología g m /I D . Con esa información, se eligen los valores para g m /I D y después se determina la corriente normalizada I D /W para cada transistor usando la gráfica mostrada en la Fig. 5. Después, con la corriente de drenaje de cada transistor la W puede ser obtenida mediante (12). Ahora bien, el diseño procede de la siguiente manera:

▪ Primero se obtiene el valor de C c usando (9), y considerando que C L = 1 pF tenemos que C cmin = 220 fF pero, para asegurar que P M > 60° se propone un mayor valor, por ejemplo C c = 500 fF.

▪ Para obtener las dimensiones de los transistores M 1,2 se determina g m1,2 usando (6), llegando a la siguiente expresión:

donde ω T = 2πf T . Nótese que el amplificador se asume que es modelado como un sistema de primer orden. De la Tabla III se tiene que f T = 100 MHz, y de acuerdo con (14) g m1,2 = 314.15 μS. Con ayuda de (8), se obtiene la corriente de polarización, I b = 40 μA, por lo tanto la corriente de drenaje requerida es I D1,2 = 20 μA, y entonces g m1,2 /I D1,2 = 15.7. Usando la información en la gráfica de la Fig. 5 se determina la corriente normalizada I D1,2 /W = 1.38, obteniendo así el ancho de canal W 1,2 = 14.76 μm.

▪ El transistor M 0 se considera que opera en la región moderada con una relación g m0 /I D0 = 15, obteniendo I D /W = 1.61 y W 0 = 25.2 μm.

▪ El espejo de corriente, formado por los transistores M 3,4 , opera en fuerte inversión con una relación g m3,4 /I D3,4 = 22, obteniendo I D /W = 2.77, y por tanto W 3,4 = 7.2 μm.

▪ Se considera que el transistor M 5 opera en la región moderada con g m5 /I D5 = 15 y I D /W = 1.61, obteniendo W 5 = 50.04 μm.

▪ Del análisis del amplificador Miller se deduce que g m6 = 5g m2 , ya que este valor puede ser relajado debido al uso del resistor R c , obteniéndose g m6 = 1.57 mS. Considerando una relación g m6 /I D6 = 20, se determina que la corriente de M 6 es I D6 = 80 μA, obteniéndose I D /W = 3.96. Con esta información se encuentra que W 6 = 20.2 μm.

3.2. Simulación y resultados

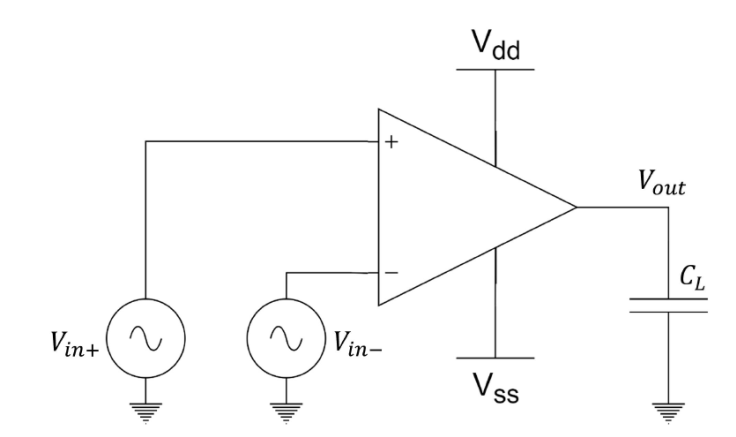

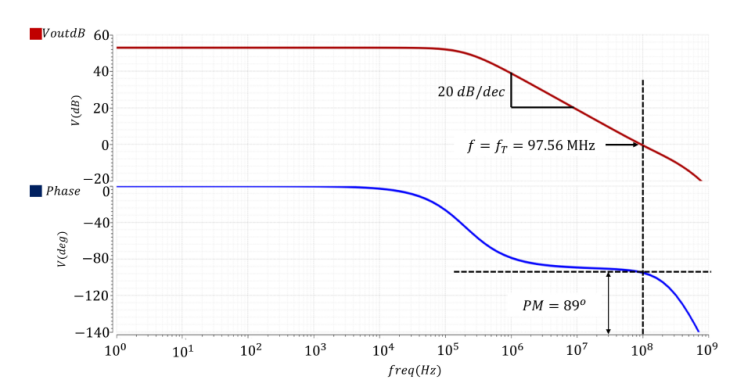

La simulación del amplificador Miller se hace en Cadence. En la Fig. 6 se muestra el circuito de prueba, que es una configuración en lazo abierto con señales de entrada V in + y V in- de igual magnitud con desfase de 180° cada una, y en la Fig. 7 se muestra la respuesta en frecuencia (en lazo abierto) de la ganancia y la fase. Esta respuesta es aceptable ya que satisface los valores de diseño propuestos en la Tabla III. Se tiene una ganancia A DC,0 = 53.29 dB y P M = 89°. El margen de fase es medido considerando que P M = 180° - fase. La fase es medida en f = f T . Si el resistor R c es retirado del circuito, el cero se desplazará a frecuencias menores, ocasionando que la fase aumente y que el PM requerido disminuya. Por esta razón, y para el dimensionamiento obtenido se utiliza R c para evitar el efecto del cero, esto es desplazándolo a frecuencias mayores a f T . Nótese que con la cancelación del cero la respuesta efectivamente se aproxima a un modelo de primer orden en el rango f ≤ f T . En la Tabla IV se muestran las dimensiones resultantes de los transistores del amplificador Miller toda vez que se realizó un ajuste. Este específicamente se realizó en las dimensiones del transistor M 5, porque el dimensionamiento original género un offset que no corresponde a las especificaciones de diseño. Por lo tanto, mediante un diseño de experimentos a nivel simulación, se hace un barrido del ancho de canal W 5 hasta alcanzar el voltaje offset y corriente I D5 requeridos.

Tabla IV Dimensiones de transistores del amplificador Miller.

| Transistor | g m /I D | Optimización |

|---|---|---|

| W 0 | 25.2 μm | 25.2 μm |

| W 1,2 | 14.76 μm | 14.76 μm |

| W 3,4 | 7.2 μm | 7.2 μm |

| W 5 | 50.04 μm | 38.52 μm |

| W 6 | 20.2 μm | 20.2 μm |

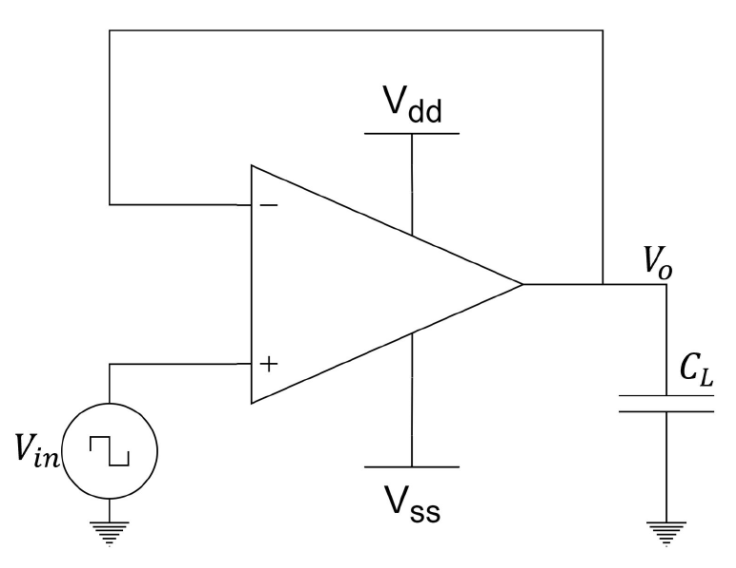

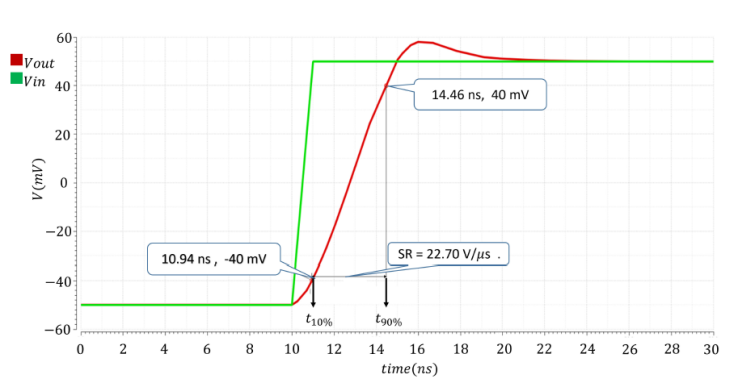

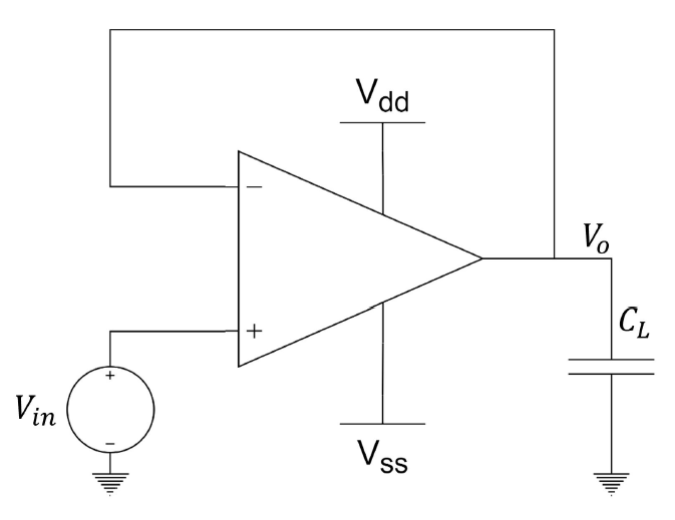

En sentido estricto hasta este punto concluye el análisis en DC, y si bien de simulación se obtienen parámetros básicos de desempeño en lazo abierto, hay otros parámetros de interés que involucra el análisis en lazo cerrado. Uno de ellos es la rapidez de respuesta, o slew rate (SR), que se puede definir como la máxima tasa de cambio en el voltaje de salida cuando el voltaje de entrada cambia de manera abrupta, y está dado en volts por microsegundo. Para cuantificar el SR, se utiliza una configuración de ganancia unitaria como se muestra en la Fig. 8. Se aplica una señal cuadrada V in = 100 mV pp con período de 1 μs y ancho de pulso de 500ñs. Para determinar el SR, se usa la siguiente aproximación:

donde ΔV

o

es la diferencia entre el 90 % de la respuesta V

o90 %

en un tiempo t

90% menos el 10 % del voltaje de salida V

o10 %

en un tiempo t

10 %; Δt es la diferencia entre los tiempos t

90 % y t

10 %. En la Fig. 9 se muestra la respuesta de salida (señal roja), donde podemos identificar a V

o10 %

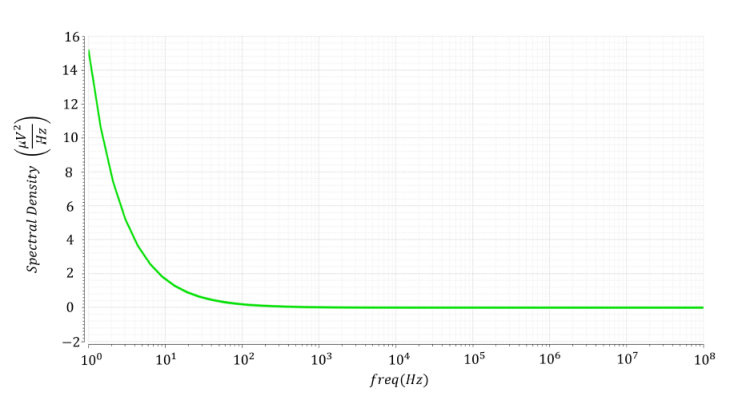

= 40 mV, t

10 % = 40 mV y t

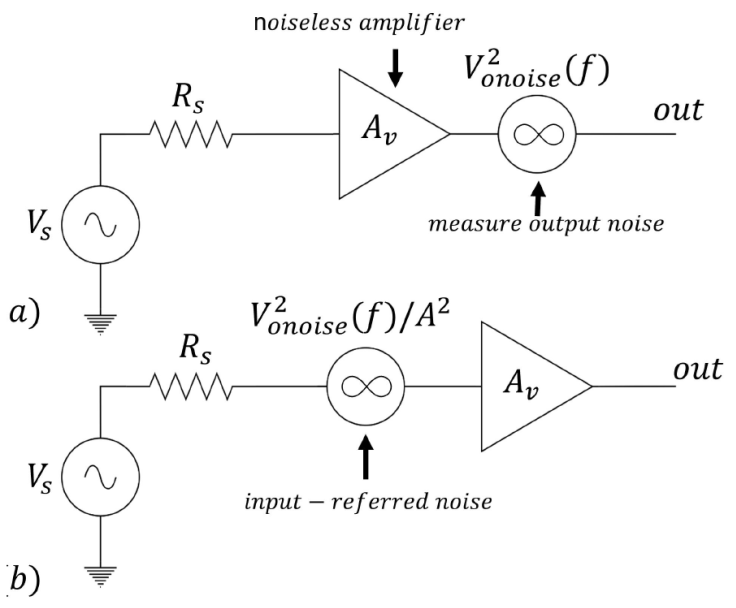

90 % = 14.46 ns, con lo cual se puede determinar que SR = 22.70 V/μs. Otro parámetro importante que puede ser analizado mediante simulación es el ruido intrínseco. Como sabemos, en muchas aplicaciones como amplificadores de audio, filtros y convertidores de datos, el ruido puede ser un factor limitante de diseño [5,16]. Un parámetro de interés es el ruido referido a la entrada (IRN, por sus siglas en inglés), el cual representa todas las fuentes de ruido intrínsecas en el circuito como una sola fuente a la entrada. En sentido estricto el ruido es medido a la salida del circuito, sin embargo, éste puede ser referido a la entrada para ser comparado con una señal de entrada. Cabe señalar que el ruido referido a la entrada no está realmente presente en la entrada del circuito bajo prueba, esta representación puede verse en la Fig. 10 [5]. En la Fig. 10a) se considera que el amplificador no genera ruido, por lo tanto, el ruido total del sistema está representado por la potencia de ruido

Figura 10 a) Medición de ruido a la salida del circuito, b) circuito hipotético de la medición del IRN.

Tabla V Parámetros de desempeño del amplificador Miller.

| Parámetro | Valor |

|---|---|

| Power Supply [V] | 1.2 |

| CMOS Technology [nm] | 130 |

| gm ef [mS] | 24.45 |

| DC gain [dB] | 53.29 |

| GBW [MHz] | 97.56 |

| Cut frequency [kHz] | 201.55 |

| PM [°] | 89 |

| SR [V/μs] | 22.70 |

| 1 % Settling Time [ns] | 10.36 |

| Cc [pF] | 0.5 |

| C L [pF] | 1 |

| I b [μA] | 40 |

| r o [kΩ] | 18.39 |

| Total current [μA] | 120 |

| Power [μW] | 144 |

| ICMR [V] | -0.27 to 0.32 |

| Input offset voltage [mV] | 0 |

| Output offset voltage [mV] | 5.2 |

| CMRR (@34 MHz) [dB] | 65.45 |

| PSRR+ (@107 kHz) [dB] | 102.9 |

| PSRR- (@200 kHz) [dB] | 109.7 |

| IRN (1 Hz - 100 MHz) [μVrms] | 39.52 |

4. Folded cascode OTA

Otro amplificador muy usado es el amplificador FC (mostrado en la Fig. 3) debido a que tiene buen desempeño en ganancia, GBW y fase [20]. El amplificador FC es de una etapa, evitando así la compensación de etapas adicionales. La idea básica es aplicar transistores cascode al par diferencial, pero utilizando transistores de tipo opuesto a los utilizados en la etapa de entrada [30]. Como se puede ver en la Fig. 3, el amplificador FC consta de un par diferencial con transistores PMOS M 1,2 y los transistores cascode NMOS M 3-M 6.

La ganancia presenta un aumento debido a los espejos de corriente cascode M3-M6 y M7-M10. La transconductancia (g m ) y la impedancia de salida r out están dominadas por diferentes transistores (M1-M9), lo que permite aumentar la ganancia sin reducir la g m , la cual afecta directamente el ancho de banda. Debido a su gran popularidad y versatilidad, en el estado del arte, diferentes trabajos muestran modificaciones a la topología original, con el fin de mejorar propiedades como ganancia, GBW y P M, por mencionar algunas [16,31,32].

4.1. Análisis en pequeña señal

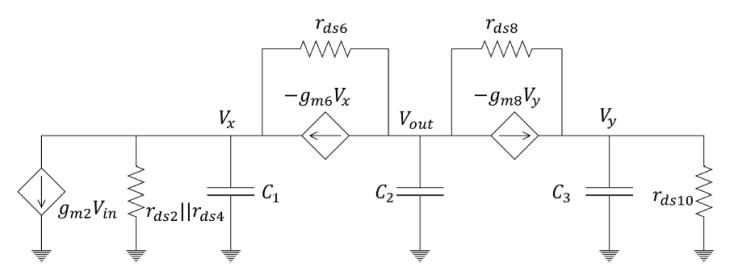

Este análisis se realiza con ayuda del circuito equivalente mostrado en la Fig. 12. La función de trasferencia H F C y la ganancia en baja frecuencia A DC,0 están dadas por (16) y (17), respectivamente:

donde g mef = g m2 es la transconductancia efectiva y la impedancia de salida está dada por:

Cada uno de los términos de la función de transferencia H F C son los siguientes:

donde C 1, C 2 y C 3 son capacitancias intrínsecas, la transconductancia g mx , transconductancia de efecto de cuerpo g mbx , conductancia g dsx , capacitancias intrínsecas C gbx , C gsx , C gdx , C bsx y C dbx están definidas en la Tabla VI. El producto ganancia-ancho de banda GBW, P M y SR, están determinadas por (25), (26) y (27), respectivamente:

4.2. Diseño con metodología g m /I D

Considerando las especificaciones de diseño (ver la Tabla III) se procede como se menciona en la Sec. 3.1, y se asume que el amplificador puede ser modelado como un sistema de primer orden.

▪ Para obtener las dimensiones de los transistores M 1,2 se determina g m1,2 usando (25):

Sabemos que f T = 100 MHz, y la corriente del transistor I D1,2 = 40 μA, por lo tanto g m1,2 = 628.31 μS y g m1,2 /I D1,2 = 15.7. Con la información de la Fig. 5 se determina que I D /W = 1.4, obteniendo así el ancho de canal del transistor W 1,2 = 29.16 μm.

▪ El transistor M 0 opera en la región de fuerte inversión con una relación g m0 /I D0 = 10, obteniendo I D /W = 4.23, y W 0 = 19.08 μm.

▪ Los transistores cascode M 3,4 , operan en moderada inversión con una relación g m3,4 /I D3,4 = 15, obteniendo I D /W = 9.06, y W 3,4 = 9 μm.

▪ Los transistores M 5,6 y M 7,8 tienen un impacto importante en la resistencia de salida r o , y también en la ganancia A DC,0 . Se propone operar en la región moderada con g m5,6 /I D5,6 = 15 y g m7,8 /I D7,8 = 15 determinando así las corrientes normalizadas (I D /W ) 5,6 = 9.06 y (I D /W ) 7,8 = 1.61. La corriente de M 5,6 y M 7,8 es I D3,4,5,6 = 40 μA, y por tanto las dimensiones son W 5,6 = 4.68 μm y W 7,8 = 25.2 μm.

▪ Se propone que M 9,10 operen en fuerte inversión con g m9,10 /I D9,10 = 6, obteniendo I D /W = 11.93. Considerando una corriente I D9,10 = 40 μA, se obtiene W 9,10 = 3.6 μm.

4.3. Simulación y resultados

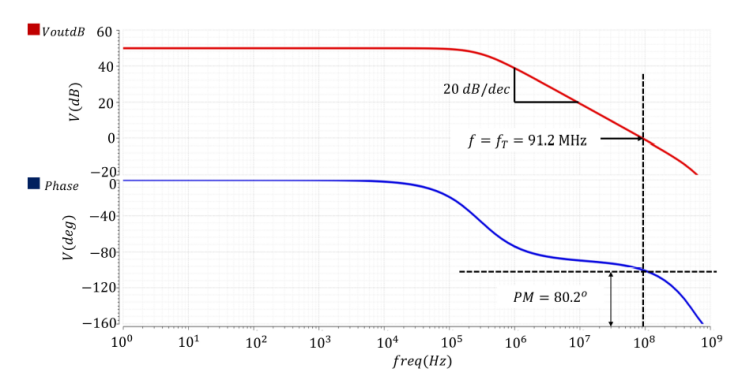

En la Tabla VII se muestran las dimensiones de los transistores del amplificador FC. La optimización se realiza ahora en las dimensiones de los transistores M 5 y M 6, debido a que el dimensionamiento original se generó un offset de salida que no corresponde a las especificaciones de diseño. Por lo tanto, con un diseño de experimentos, se hace un barrido del ancho de canal W 5 y W 6 hasta alcanzar el voltaje offset y corrientes I D5 y I D6 requeridos. Como hemos visto, el dimensionamiento de los transistores es primordial en el diseño de amplificadores CMOS, y por tanto presenta un impacto en los parámetros del mismo. La Fig. 13 muestra la respuesta en frecuencia en lazo abierto (ganancia y fase), donde se observa que A DC,0 = 50 dB, P M = 80.2 y GBW = 91.2 MHz son valores que cumplen las especificaciones de diseño. Nótese que efectivamente el amplificador es un sistema de primer orden:

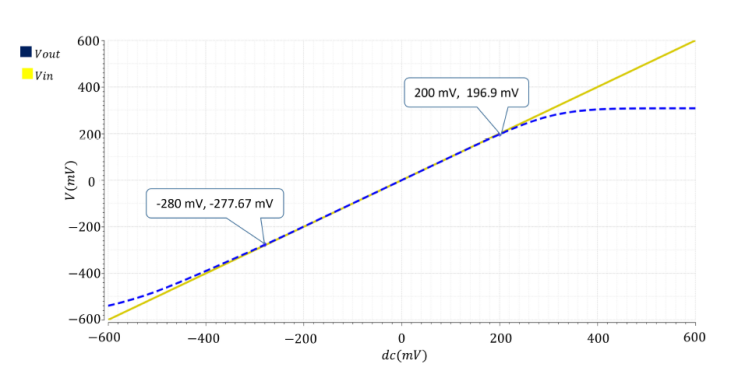

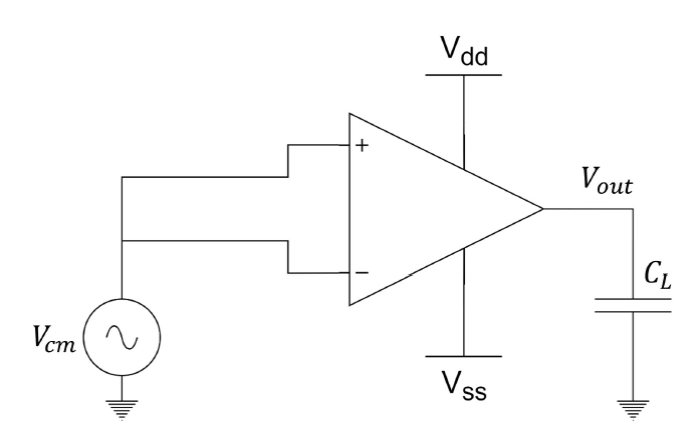

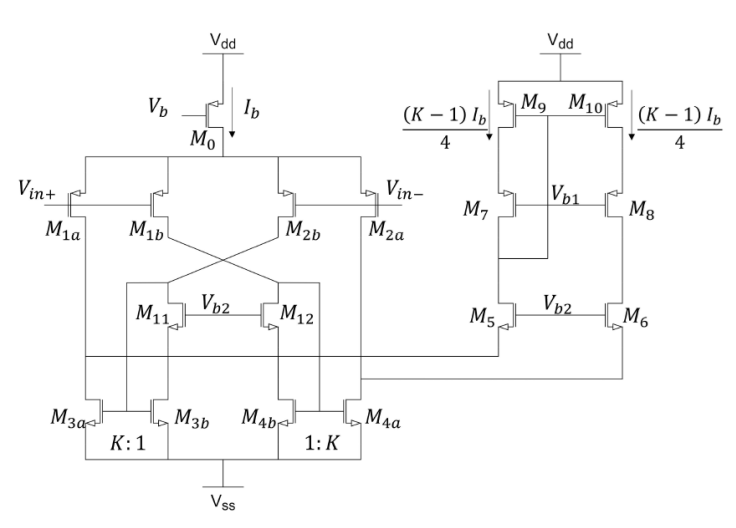

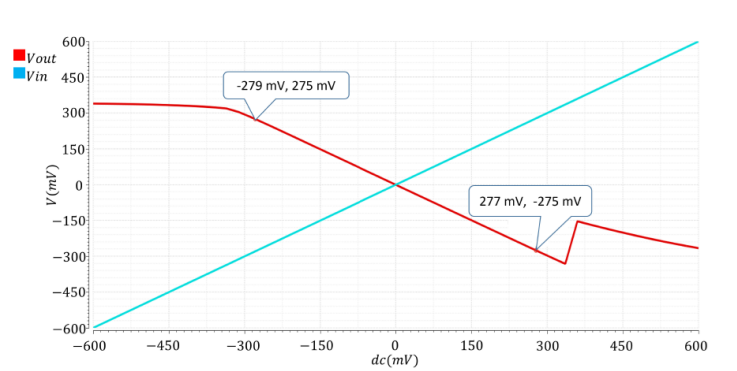

donde ω p es el polo dominante. Otro de los parámetros que presenta relación con la ganancia del amplificador, es el rango de voltaje de entrada en modo común (ICMR por sus siglas en inglés), y se define como el rango de voltaje de entrada en modo común hasta el cual los transistores asociados a la entrada diferencial (M 1,2 ) están en saturación y dan una ganancia constante [4,5,21]. Para medir el ICMR se utiliza la configuración de ganancia unitaria, mostrada en la Fig. 14. Se realiza un barrido de la señal de entrada V in de -600 mV a 600 mV para obtener la respuesta mostrada en la Fig. 15. Aquí se muestra la parte lineal de la curva de transferencia donde la pendiente es la unidad, que corresponde al rango de -280 mV a 200 mV, y define el rango de voltaje ICMR. Otro parámetro importante que puede ser analizado es la razón de rechazo en modo común (CMRR, por sus siglas en inglés), que se puede definir como la habilidad que presenta el amplificador diferencial para rechazar una señal común aplicada a la entrada. El CMRR se puede expresar como la relación de la ganancia en modo diferencial (V DM ) con la ganancia en modo común (VCM ) [5]:

Para cuantificar este parámetro, se utiliza una configuración en lazo abierto (mostrada en la Fig. 6) para obtener la respuesta en modo diferencial, y para la respuesta en modo común se utiliza la configuración mostrada en la Fig. 16, la cual presenta una señal de entrada en modo común V cm . La respuesta se muestra en la Fig. 17, y corresponde a un valor de 75.46 dB para f < 3.9 MHz. En la Tabla VIII se resume el rendimiento del amplificador FC.

Tabla VII Dimensiones de transistores del amplificador FC.

| Transistor | g m /I D | Optimización |

|---|---|---|

| W0 | 19.08 μm | 19.08 μm |

| W1,2 | 29.16 μm | 29.16 μm |

| W 3,4 | 9 μm | 9 μm |

| W 5,6 | 4.68 μm | 18.72 μm |

| W 7,8 | 25.2 μm | 25.2 μm |

| W 9,10 | 3.6 μm | 3.6 μm |

5. Recycling folded cascode

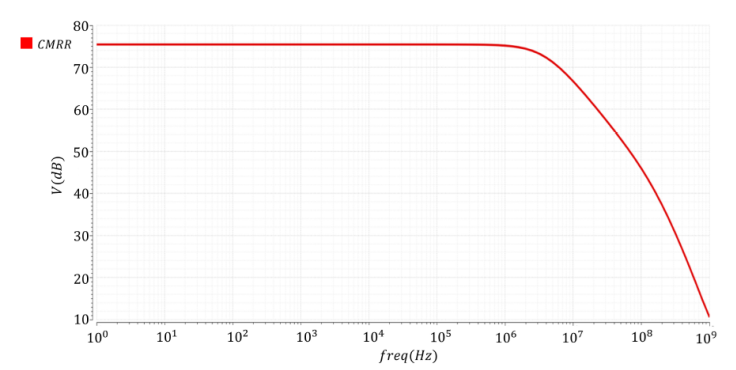

En la arquitectura mostrada en la Fig. 3 se observa que los transistores M 3 y M 4 conducen una corriente I b , lo cual representa la mayoría de la corriente consumida, y esto es motivo de que estos transistores en ocasiones presenten una transconductancia de valor grande. Sin embargo, su propósito sólo se limita a proporcionar un nodo folded para la corriente en pequeña señal generada por los transistores M 1,2, que es la característica principal de este amplificador. Considerando esto como una ineficiencia del FC, debido a que la utilidad de los transistores M 3 y M 4 no se aprovecha totalmente, se propone en Ref. [16] la arquitectura del amplificador recycling folded cascode (RFC) mostrada en la Fig. 18, donde se explica que las modificaciones realizadas al FC convencional fue para usar los transistores M 3 y M 4 como transistores de conducción, lo que permite un control de la señal de entrada y de la corriente de polarización. Se observa que los transistores M 1 y M 2 se dividen al 50 % del ancho de canal W, generando M 1a , M 1b , M 2a y M 2b , los cuales conducirán una corriente I b /4. Los transistores M 3 y M 4 se dividen para generar los espejos de corriente M 3a : M 3b y M 4a : M 4b con una relación K:1. La conexión cruzada de los espejos de corriente aseguran que las corrientes de pequeña señal proporcionadas a los transistores M 5 y M 6 estén en fase. Los transistores M 11 y M 12 se dimensionan igual a M 5 y M 6.

Tabla VIII Parámetros de desempeño del amplificador FC.

| Parámetro | Valor |

|---|---|

| Power Supply [V] | 1.2 |

| CMOS Technology [nm] | 130 |

| gm ef [μS] | 637.40 |

| DC gain [dB] | 50 |

| GBW [MHz] | 91.20 |

| Cut frequency [kHz] | 291.49 |

| PM (°) | 80.2 |

| SR [V/μs] | 21.82 |

| 1 % Settling Time [ns] | 7.92 |

| C L [pF] | 1 |

| I b [μA] | 80 |

| r o [kΩ] | 519 |

| Total current [μA] | 160 |

| Power [μW] | 192 |

| ICMR [V] | -0.28 to 0.20 |

| Input offset voltage [mV] | 0 |

| Output offset voltage [mV] | 19.93 |

| CMRR (@3.9 MHz) [dB] | 75.46 |

| PSRR+ (@289 kHz) [dB] | 91.98 |

| PSRR- (@289 kHz) [dB] | 86.49 |

| IRN (1Hz - 100 MHz) [μV rms ] | 58.64 |

5.1. Analisis en pequena senal

El análisis es igual al del FC, del cual se obtiene una función de transferencia similar a (16), donde se intercambia la transconductancia g m2 por g m2a . También se intercambian las conductancias g ds2 y g ds4 por g ds2a y g ds4a , respectivamente, donde K es la ganancia de corriente del espejo de corriente [16]. En (31) y (32) se muestra la transconductancia efectiva del amplificador RFC y la impedancia de salida, respectivamente.

De la Fig. 18 se observa que la corriente a través de M 5-M 10 es función de K. En la Ref. [16] se menciona que para conservar la potencia y área iguales al amplificador FC, K debe ser igual a 3. Los parámetros GBW y SR están dados, respectivamente, por

5.2. Diseño con metodología g m /I D

Para el diseño del amplificador RFC, el método aquí descrito parte del diseño de un amplificador FC visto en la Sec. IV.

▪ Para el amplificador FC, de acuerdo a la Ref. [16], los transistores M 1a , M 2b , M 1b y M 2b deben tener un tamaño igual a W 1,2 /4 ≈ 7.56 μm.

▪ De las dimensiones de M 3,4 del FC, se obtienen las dimensiones de M 3a,3b y M 4a,4b considerando un valor K = 3, consiguiendo W 3a,4a = 7.56 μm y W 3b,4b = 2.52 μm.

▪ Las dimensiones de M 11 y M 12 son iguales a los transistores M 5 y M 6, respectivamente.

▪ Los transistores M 0, M 7, M 8, M 9 y M 10 conservan las mismas dimensiones del amplificador FC.

5.3. Simulación y resultados

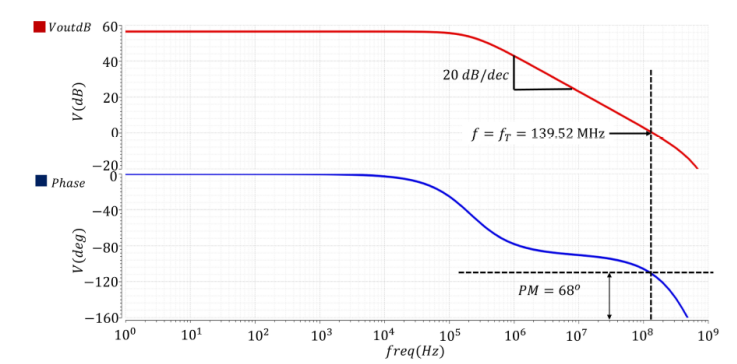

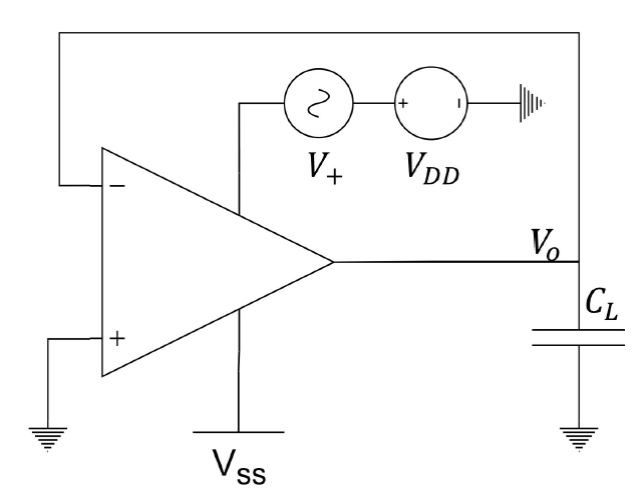

La Fig. 19 muestra la respuesta en frecuencia en lazo abierto de la ganancia y fase, donde se observa que A DC,0 = 56.5 dB, P M = 68° y GBW = 139.52 MHz son valores que cumplen con las especificaciones de diseño, y en efecto puede modelarse como un sistema de primer orden. Como se ha visto en la Secs. 3 y 4, el ruido y voltaje en modo común pueden afectar la respuesta esperada del amplificador, y ello lleva a cambios en los parámetros de diseño, los cuales son efectos no deseados. Por eso es importante considerar todos los componentes que son conectados al amplificador, entre estos están las fuentes de alimentación (V DD , V SS , GND), las cuales también aportan variaciones o ruido a la respuesta. Por lo tanto es importante realizar un análisis del factor de rechazo de la fuente de alimentación (PSRR, por sus siglas en inglés), que se define como el producto de la relación entre el cambio de la fuente de alimentación y el cambio en el voltaje de salida del amplificador causado por el cambio en la fuente de alimentación y la ganancia en lazo abierto del amplificador. En otras palabras, indica qué tan bien responde el amplificador a las variaciones de la fuente de alimentación (positiva y negativa). Esto se representa mediante:

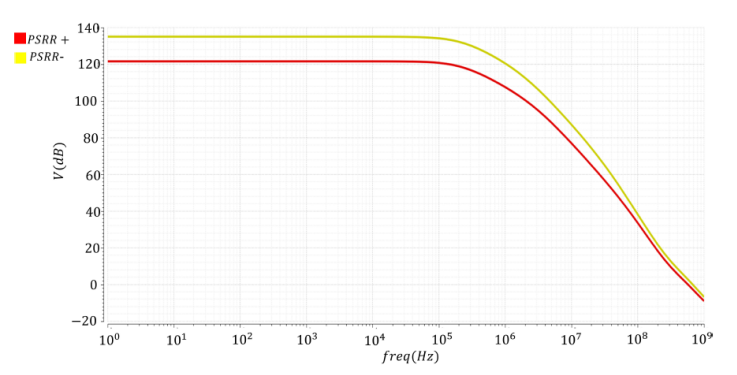

donde V OL es la magnitud del voltaje de salida del amplificador; V + y V - corresponden a los cambios en la fuente de alimentación positiva y negativa, respectivamente. Para determinar el PSRR + se usa la configuración de la Fig. 20, donde se observa que una señal en AC es conectada en serie con V DD (en el caso del PSRR ¡ , se conecta una señal AC en serie con V SS ), y mediante un análisis en AC se obtiene la respuesta correspondiente a la relación V o /V +. Sabemos que A DC,0 = 56.5 dB, entonces con ayuda del simulador se resuelve (35) y se obtiene la respuesta PSRR + mostrada en la Fig. 21. En la Tabla IX se muestran las dimensiones de los transistores del amplificador RFC, y en la Tabla X se resume su rendimiento, donde se puede ver un mejor desempeño de los parámetros en comparación con el amplificador FC.

Tabla IX Dimensiones de transistores del amplificador RFC.

| Transistor | g m /I D |

|---|---|

| W 0 | 19.08 μm |

| W 1a,1b | 7.56 μm |

| W 2a,2b | 7.56 μm |

| W 3a,4a | 7.56 μm |

| W 3b,4b | 2.52 μm |

| W 5,6 | 18.72 μm |

| W 7,8 | 25.2 μm |

| W 9,10 | 3.6 μm |

| W 11,12 | 18.72 μm |

Tabla X Parámetros de desempeño del amplificador RFC.

| Parámetro | Valor |

|---|---|

| Power Supply [V] | 1.2 |

| CMOS Technology [nm] | 130 |

| gm ef [mS] | 1 |

| DC gain [dB] | 56.50 |

| GBW [MHz] | 139.52 |

| Cut frequency [kHz] | 214.04 |

| PM [°] | 68 |

| SR [V/μs] | 41.96 |

| 1 % Settling Time [ns] | 4.61 |

| C L [pF] | 1 |

| I b [μA] | 80 |

| r o [kΩ] | 668.34 |

| Total current [μA] | 160 |

| Power [μW] | 192 |

| ICMR [V] | -0.33 to 0.43 |

| Input offset voltage [mV] | 0 |

| Output offset voltage [mV] | 27.54 |

| CMRR (@2.9 MHz) [dB] | 76.20 |

| PSRR+ (@212 kHz) [dB] | 121.62 |

| PSRR- (@212 kHz) [dB] | 135.00 |

| IRN (1Hz - 100 MHz) [μVrms ] | 59.67 |

6. Amplificador de dos etapas con compensación feedforward

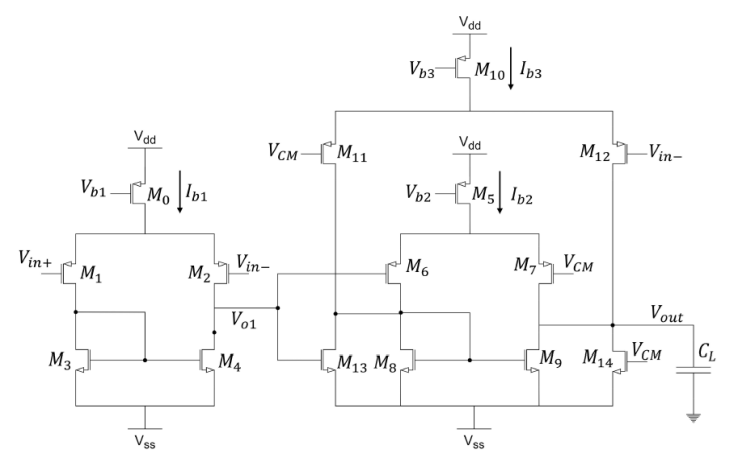

En los amplificadores CMOS es complicado obtener un diseño de alta ganancia y un amplio ancho de banda porque éstos y otros parámetros (potencia, impedancia de salida, ruido, etc) se relacionan entre sí, haciendo del diseño un problema de optimización multidimensional [4]. Entonces, se pueden identificar amplificadores multi-etapa que son diseñados para tener una ganancia grande usando transistores polarizados con un bajo nivel de corriente. Y también están los amplificadores con un amplio ancho de banda que usan etapas simples con transistores polarizados con un alto nivel de corriente. Para aprovechar las ventajas de cada una de estas arquitecturas, existen amplificadores como el amplificador de dos etapas con compensación Miller (ver Fig. 2) visto en la Sec. 2. Como sabemos, en un amplificador Miller, el polo dominante es desplazado hacia frecuencias bajas debido al efecto del pole-splitting, resultando en estructuras de alta ganancia, adecuada compensación de fase, pero de menor ancho de banda. Entonces, para evitar este inconveniente en la Ref. [22] se propone y se explica un esquema de compensación feedforward (CFF) para amplificadores multi-etapa sin usar capacitores de compensación. La arquitectura propuesta es un amplificador de dos etapas con CFF [22,33] que se muestra en la Fig. 22. Se observa que tanto la primer (M 0-M 4) como la segunda etapa (M 5-M 9) son un par diferencial de salida simple, y la etapa feedforward está implementada por los transistores M 10 - M 14. Este esquema usa un corrimiento de fase positivo de los ceros ubicados en el semiplano derecho, generados mediante una ruta feedforward para compensar el corrimiento de fase negativa de los polos. El par polo-cero es situado en frecuencias grandes para evitar componentes de establecimiento lentos asociados con la cancelación polo-cero a bajas frecuencias, lo cual ocasiona que el polo dominante (ubicado en frecuencias menores al segundo polo) sea cancelado junto con el cero [22,34]. Otra ventaja de este amplificador es que evita al capacitor de compensación, y así reducir espacio de integración y obtener mejoras en la corrección del P M, A DC,0 y GBW [22].

6.1. Análisis en pequeña señal

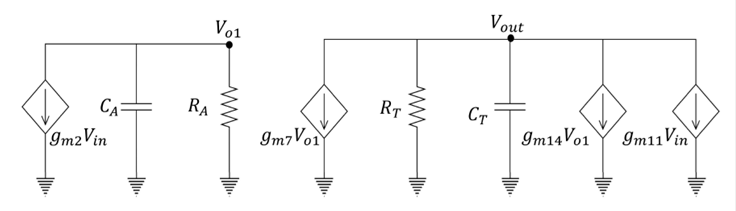

El análisis se realiza con ayuda del circuito equivalente mostrado en la Fig. 23. La función de transferencia H CFF y la ganancia en baja frecuencia A DC,0 están dadas por (37) y (38), respectivamente.

Se observa que (37) es una función de segundo orden con un cero, donde ω p1 , ω p2 y ω z son los polos y cero del sistema definidos por (39), (40) y (41), respectivamente.

aquí A V A , A V B y A V C son ganancias en baja frecuencia de la primer etapa, segunda etapa y compensación feedforward, definidas por (42), (43) y (44), respectivamente.

de las ecuaciones anteriores C A es la capacitancia equivalente de la primer etapa del amplificador, y por último R A y R T son impedancias equivalentes, que están definidas en la Tabla XI.

Considerando (42), (43) y (44) se puede representar a (38) como sigue:

donde g mef es la transconductancia efectiva y r o la impedancia de salida, que se definen como:

Los amplificadores son utilizados en configuraciones de lazo cerrado con capacitores de retroalimentación, como el que se muestra en la Fig. 24. En estos casos una cancelación polo-cero puede no llevarse a cabo satisfactoriamente, debido a una doble aparición de un polo-cero. Por lo cual en la Ref. [22] se desarrolla un análisis del circuito, obteniendo una optimización de las Ecs. (37)-(41). Para una explicación más detallada es recomendable la lectura de [22]. Las ecuaciones de diseño optimizadas para este amplificador y garantizar la cancelación de ω p1 y ω z se definen como sigue:

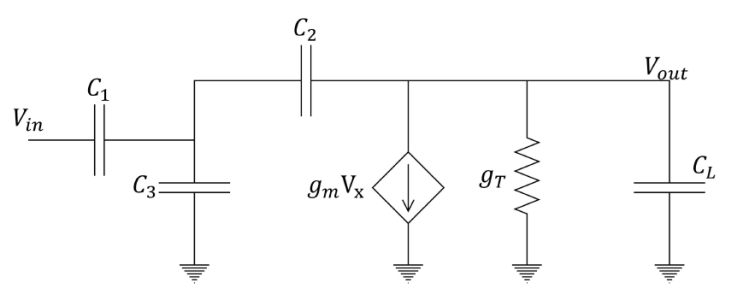

donde β= C 2 /(C 1 + C 2 + C 3) es el factor de retroalimentación y g T = 1/(R T ). Entonces, podemos observar que ω p1 y ω z deben ser muy próximos entre sí, sin importar el valor de las capacitancias [22]. Si se reduce el valor de la capacitancia intrínseca C A (salida de la primer etapa), incrementa la frecuencia de ω p1 y ω z , y la cancelación polo-cero ocurre en altas frecuencias ocasionando que la frecuencia esté controlada por ωp2 y así tener un amplio ancho de banda.

6.2. Diseño con metodología g m /I D

Como se menciona en la Ref. [22], el amplificador de dos etapas con CFF debe satisfacer las siguientes consideraciones de diseño:

▪ La segunda etapa y la compensación feedforward no deben tener ningún polo antes del GBW; se asume que el amplificador se modelará como un sistema de primer orden.

▪ La cancelación de los polos y ceros deben ocurrir en altas frecuencias.

▪ La ganancia en DC del amplificador debe ser alta.

Estas condiciones se pueden alcanzar si las etapas se escogen como sigue:

▪ Para la primer etapa es recomendable que sea diseñada para tener una ganancia alta y una capacitancia pequeña como carga.

▪ La segunda etapa y la compensación feedforward deben estar optimizadas para obtener un ancho de banda grande y una ganancia media.

Considerando los puntos anteriores, el proceso de diseño del amplificador de dos etapas con CFF, es como sigue:

▪ Como se observa en la Fig. 22, la primer etapa está formada por los transistores M 0-M 4, la cual es crucial para el diseño de todo el amplificador, ya que de ésta se basa el diseño de la segunda etapa y de la compensación feedforward. Considerando las especificaciones de diseño y las propias de esta arquitectura, se considera como capacitancia de carga de la primer etapa C L1 = 250 fF. Mediante (51) se calcula la corriente de polarización I b1 = 20 μA:

▪ Para el transistor M 0 se considera g m0 /I D0 = 10, con ayuda de la información en la Fig. 5, se obtiene I D =W = 4.61. Conociendo que I b1 = 20 μA y usando (12) se obtiene W 0 = 4.68 μm.

▪ Se considera que los transistores M 1,2 tengan un valor g m1,2 /I D1,2 = 20, obteniendo I D /W = 0.44, y por tanto W 1,2 = 23:04 μm.

▪ Es de importancia que los voltajes offset de entrada y salida sean del mismo valor, con el fin de que los transistores de entrada de las siguientes etapas estén polarizados adecuadamente. Por tal motivo los transistores M 3,4 se consideran operen en fuerte inversión con g m3,4 /I D3,4 = 4.62, obteniendo I D /W = 65.24, y por tanto W 3,4 = 324 nm. Con este valor de W 3,4 el voltaje offset de salida no alcanza a ser el mismo valor de voltaje offset de entrada, por lo tanto se elige un valor W 3,4 = 180 nm para alcanzar un valor de 0 V.

▪ Para la segunda etapa (transistores M 5 - M 9) se utilizan las mismas dimensiones obtenidas en la primer etapa. Recordando que la segunda etapa debe tener una corriente I b2 mayor a I b1 para alcanzar un mayor ancho de banda, se utiliza una multiplicidad M M2 = 10 para todos los transistores de la segunda etapa y así alcanzar una corriente de polarización I b2 = 200 μA.

▪ La etapa de compensación feedforward se determina haciendo un barrido mediante una serie de simulaciones, para obtener una corriente I b3 = 800 μA y alcanzar un PM ≈ 90°. Por lo tanto, para los transistores M 10 - M 14 se utiliza una multiplicidad M M3 = 40.

6.3. Simulación y resultados

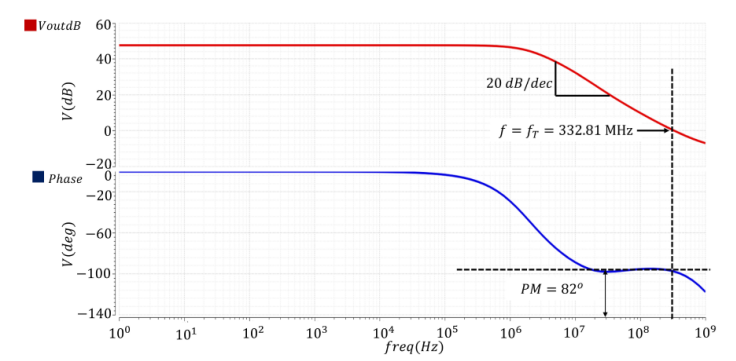

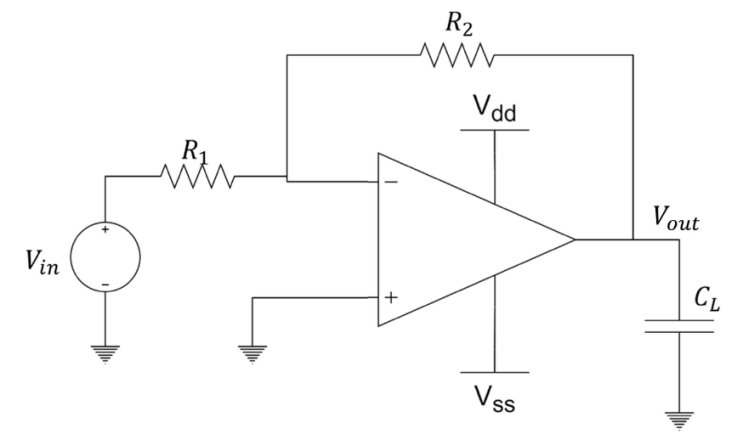

La Fig. 25 muestra la respuesta en frecuencia en lazo abierto (de la ganancia y la fase), donde se observa que A DC,0 = 47:64 dB, P M = 82° y GBW = 332.81 MHz son valores que cumplen con las especificaciones de diseño, y en efecto puede modelarse como un sistema de primer orden. Otro parámetro que se caracteriza mediante simulación es el output swing, el cual define qué tan cercana es la oscilación de la señal de salida a los voltajes de alimentación (V DD y V SS ) [5,4,30]. Este se determina con el circuito mostrado en la Fig. 26, que es una configuración de un amplificador inversor, el cual cuenta con dos resistores R 1 y R 2, un capacitor de carga C L y una fuente de entrada V in, la cual realiza un barrido de -600 mV a 600 mV. La respuesta se muestra en la Fig. 27, donde la curva de transferencia entre V in y V out representa el output swing ubicando los voltajes máximo V omáx = 275 mV y mínimo V omín = -275 mV de salida del amplificador. En la Tabla XII se muestran las dimensiones de los transistores y la multiplicidad de cada uno de éstos, y en la Tabla XIII el rendimiento del amplificador CFF.

Tabla XII Dimensiones de transistores del amplificador CFF.

| Transistor | g m /I D | Multiplicidad |

|---|---|---|

| W 0 | 4.68 μm | 1 |

| W 1,2 | 23.04 μm | 1 |

| W 3,4 | 180 nm | 1 |

| W 5 | 4.68 μm | 10 |

| W 6,7 | 23.04 μm | 10 |

| W 8,9 | 180 nm | 10 |

| W 10 | 4.68 μm | 40 |

| W 11,12 | 23.04 μm | 40 |

| W 13,14 | 180 nm | 40 |

Tabla XIII Parámetros de desempeño del amplificador CFF.

| Parámetro | Valor |

|---|---|

| Power Supply [V] | 1.2 |

| CMOS Technology [nm] | 130 |

| gm ef [mS] | 124.48 |

| DC gain [dB] | 47.64 |

| GBW [MHz] | 332.81 |

| Cut frequency [kHz] | 1889 |

| PM [°] | 82 |

| SR [V/μs] | 42.53 |

| 1 % Settling Time [ns] | 8.71 |

| C L (pF) | 1 |

| I b1 [μA] | 22 |

| I b2 [μA] | 222 |

| I b3 [μA] | 885 |

| Total current [μA] | 1129 |

| r o [kΩ] | 1.94 |

| Power [μW] | 1354 |

| ICMR [V] | 0.05 to 0.43 |

| Input offset voltage [mV] | 0 |

| Output offset voltage [mV] | 3.31 |

| CMRR (@2.9 MHz) [dB] | 47.7 |

| PSRR+ (@1.3 MHz) [dB] | 67 |

| PSRR- (@1.8 MHz) [dB] | 46.56 |

| IRN (1Hz - 100 MHz) [μV rms ] | 72.95 |

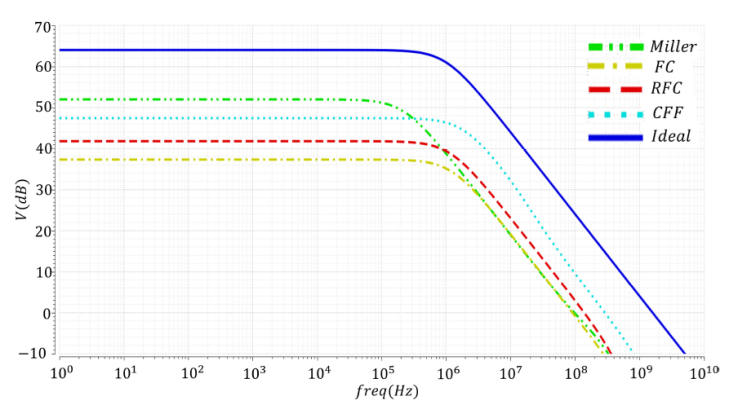

7. Comparación de amplificadores

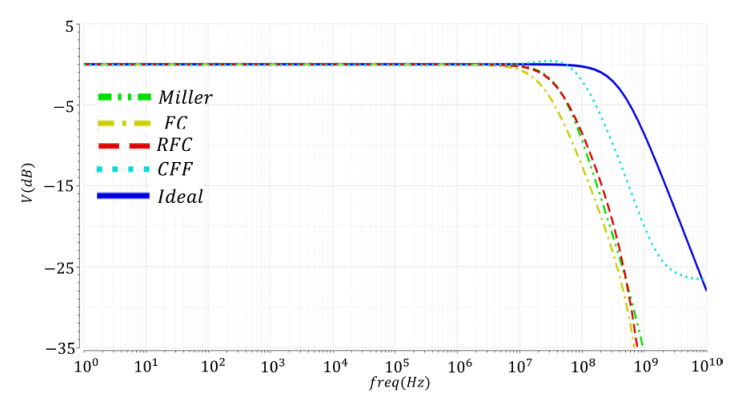

Los amplificadores son parte importante en el diseño analógico de circuitos integrados, y cada topología presenta distintas características que resultan adecuadas para diferentes aplicaciones. En la Tabla XIV se muestra la comparación de parámetros de desempeño de los amplificadores diseñados con las características de desempeño mostradas en la Tabla III. La mayor transconductancia efectiva se presenta en el amplificador CFF con g mef = 124.29 mS, sobrepasando por mucho al amplificador FC que cuenta con g mef = 637 μS. La mayor ganancia se obtuvo con RFC, A DC,0 = 56.5 dB, mostrando que es mejor alternativa al amplificador FC que muestra A DC,0 = 49.9 dB. El ancho de banda de los amplificadores FC y Miller es cercano al indicado en la Tabla III, con 91.2 MHz y 97.56 MHz, respectivamente, y los amplificadores RFC y CFF lo sobrepasan (139.52 MHz y 332.81 MHz, respectivamente). Estos últimos también son los que presentan un mayor SR con 41.96 V/μs y 42.53 V/μs, respectivamente. El amplificador con mayor impedancia de salida es el RFC con r o = 668.34 kΩ y el que presenta menor impedancia es el CFF con r o = 2.57 kΩ. Como sabemos, la corriente de drenaje es directamente proporcional a las dimensiones del transistor (13), por lo cual el amplificador con mayor consumo de corriente es el CFF con 124.29 mA. Los amplificadores FC y RFC consumen la misma corriente (160 μA), con lo cual se puede confirmar un mejor rendimiento y eficiencia de potencia del RFC sobre el FC. El amplificador Miller consume una corriente total de 120 μA. Este último presenta la menor potencia consumida con 144 μW.

Tabla XIV Tabla comparativa de parámetros de diseño de amplificadores.

| Parámetros | Miller | FC | RFC | CFF |

|---|---|---|---|---|

| Power Supply [V] | 1.2 | 1.2 | 1.2 | 1.2 |

| CMOS Technology [nm] | 130 | 130 | 130 | 130 |

| gm ef [mS] | 24.45 | 0.637 | 1 | 124.29 |

| DC gain [dB] | 53.29 | 49.9 | 56.5 | 47.64 |

| GBW [MHz] | 97.56 | 91.2 | 139.52 | 332.81 |

| PM [°] | 89 | 80.2 | 68 | 82 |

| SR [V/μs] | 22.70 | 21.82 | 41.96 | 42.53 |

| C L [pF] | 1 | 1 | 1 | 1 |

| I b [μA] | 40 | 80 | 80 | - |

| I b1 [μA] | - | - | - | 22 |

| I b2 [μA] | - | - | - | 222 |

| I b3 [μA] | - | - | - | 885 |

| r o [kΩ] | 18.39 | 519 | 668.34 | 1.94 |

| Total current [μA] | 120 | 160 | 160 | 1129 |

| Power [μW] | 144 | 192 | 192 | 1354 |

El análisis de los amplificadores muestra diferentes valores de ancho de banda, ganancia, fase y velocidad de respuesta como parámetros críticos de diseño, así como un área de diseño y consumo de energía específicos. Es importante señalar que, para la metodología aquí descrita, si se reduce al 50 % el ancho de todos los dispositivos, los amplificadores ocupan el 50 % de área y usan el 50 % de la corriente de polarización, lo cual lleva a un menor consumo de potencia, pero también el ancho de banda y la velocidad de respuesta presentan una reducción aproximada del 50 %.

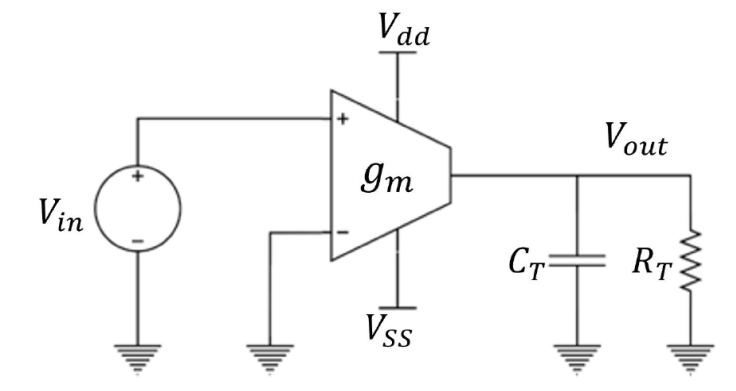

Para realizar una comparación de la utilidad general de los amplificadores, suponer que es de interés hacer la síntesis de un filtro pasa-bajas, que se muestra en la Fig. 28 [35], y suponer que se desea una frecuencia de corte en 1.0 MHz. El circuito es un integrador o filtro pasa-bajas con pérdida, cuyo polo es determinado por el reciproco del producto R T C T .

La función de transferencia que describe el comportamiento del integrador es

y la frecuencia de corte está definida por

donde g m es la transconductancia efectiva del amplificador, R T = r o ||R L es el paralelo de la impedancia de salida r o y la impedancia de carga R L , y C T = C o + C L es la suma de la capacitancia intrínseca de salida C o y la capacitancia de carga C L . Si R L = 159 kΩ y C L = 1 pF nótese que el primer factor en (53) corresponde a una frecuencia f c = 1 MHz, sin embargo porque cada amplificador tiene diferente impedancia de salida, el segundo factor provocará un corrimiento de f c que depende del amplificador usado (ver Tabla XV), y otro factor de corrimiento es el efecto de C o mostrado también en Eq. (53). El desempeño del integrador se muestra en la Fig. 29, y en la Tabla XV se presenta el valor de la frecuencia de corte obtenida y el porcentaje en el corrimiento obtenido. De acuerdo a la Tabla XV los amplificadores que más se acercaron a 1 MHz fueron FC y RFC, debido a sus altas impedancias de salida r o = 519 kΩ y r o = 668.34 kΩ, respectivamente. Los amplificadores Miller y CFF, siendo amplificadores de dos etapas, mostraron un corrimiento mayor debido a su menor impedancia de salida con r o = 18.39 kΩ y 2.57 kΩ, respectivamente. Nótese que otro efecto de corrimiento ocurre con la ganancia:

Tabla XV Comparación entre respuestas del filtro pasa-bajas con pérdida.

| Amplificador | fc (MHz) | Corrimiento |

|---|---|---|

| Miller | 0.22 | 77.80 % |

| FC | 1.24 | 23.70 % |

| RFC | 1.16 | 15.80 % |

| CFF | 1.88 | 88.00 % |

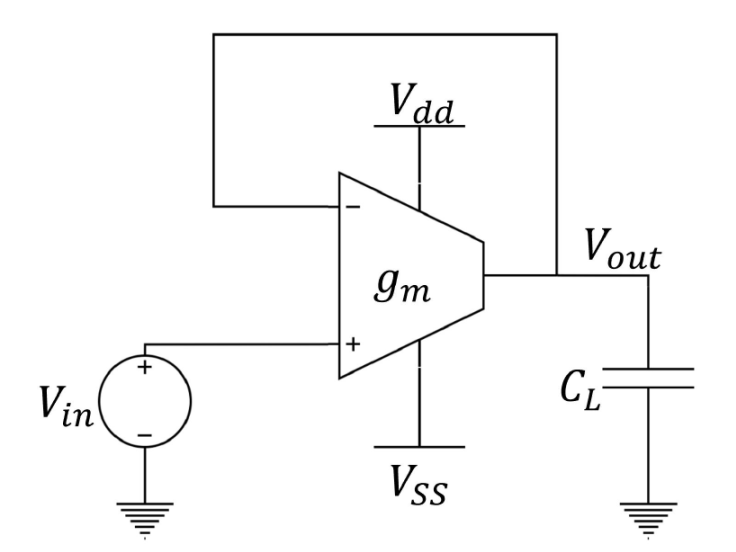

Lo anterior muestra que las características del amplificador deben tomarse en cuenta en la síntesis. Una configuración donde sólo se requiera controlar la posición del polo, es mostrada en la Fig. 30, cuya función de transferencia y frecuencia de corte son:

donde g mef es la transconductancia efectiva, r o es la impedancia de salida y C L la capacitancia de carga. Esta opción de diseño no sólo omite el uso de un resistor sino que, considerando el valor de g mef y r o , se define el valor de C L y tener la frecuencia de corte requerida. Con esta estrategia cualquier amplificador puede ser usado, se reduce el área de integración y se elimina una potencial fuente de ruido térmico. Para un valor de capacitancia fijo, C L = 1 pF, la respuesta se muestra en la Fig. 31, donde la frecuencia f c es el único parámetro variable. Es importante señalar que la respuesta de los amplificadores multi-etapa presentan un mayor corrimiento en frecuencia en comparación al esperado, debido a que presentan más elementos que intervienen en el comportamiento de la función de transferencia, por lo que también es válido tomar ventaja del simulador e inferir la capacitancia C o . Por ejemplo, para el amplificador Miller debe considerarse la condición de estabilidad (9), lo que indica que el capacitor C c también debe cambiar para un determinado C L . Para el caso de obtener una frecuencia f c = 1 MHz, usando (56) se obtienen valores de C L muy grandes (Miller = 3.89 nF, FC = 101 pF, RFC = 159 pF, CFF = 19.78 nF) lo cual hace inconsistente su implementación, ya que el espacio de diseño sería muy grande y es un punto crítico que debe evitarse. Por lo tanto, de acuerdo al comportamiento observado en el filtro pasa-bajas, puede verificarse que al no considerar parámetros básicos de cada amplificador (g m y r o ), la respuesta del filtro es diferente, lo que demuestra que el amplificador debe ser diseñado a la medida de la aplicación.

8. Conclusiones

Se presentó la descripción y análisis de los amplificadores Miller, FC, RFC y CFF, de los cuales se mostró su aproximación a un sistema de primer orden. También se presentó la metodología g m /I D como una alternativa al diseño de amplificadores CMOS utilizando curvas de desempeño de parámetros del transistor usando directamente la tecnología de fabricación (para este trabajo se utilizó una tecnología CMOS de 130 nm). Se determinó que con la aproximación de un sistema de primer orden de los amplificadores se puede utilizar la metodología g m /I D de una manera sencilla y práctica para el diseño, específicamente para el dimensionamiento de transistores (NMOS y PMOS). También se mostró la medición, mediante simulación, de diferentes parámetros de desempeño mediante el uso de diferentes configuraciones del amplificador. Sabemos que los amplificadores son parte importante en el diseño de circuitos analógicos y en este trabajo se mostró que cada topología presenta distintas características que son adecuadas para diferentes aplicaciones. Se realizó un circuito pasa-bajas en lazo abierto y lazo cerrado, donde se muestra el efecto de los parámetros fundamentales (g m y r o ) del amplificador en el cual puede verificarse que al no considerar estos parámetros básicos, la respuesta del filtro es diferente, lo que demuestra que no es el amplificador el que se ajusta a una aplicación sino que la aplicación impone las características de desempeño al amplificador, y justifica por qué su diseño es a la medida.

nueva página del texto (beta)

nueva página del texto (beta)