Control de un rectificador PWM con funciones ampliadas basado en un procesador digital de señales

Control of a PWM Rectifier with Extended Functions in a Signal Digital Processor

C. Núñez–Gutiérrez1, J. Lira–Pérez2, V.M. Cárdenas–Galindo3 y R. Alvarez–Salas4

1 Centro de Investigación y Estudios de Posgrado, Facultad de Ingeniería (CIEP) Universidad Autónoma de San Luis Potosí. México. E–mail: calberto@uaslp.mx

2 Centro de Investigación y Estudios de Posgrado, Facultad de Ingeniería (CIEP) Universidad Autónoma de San Luis Potosí. México. E–mail: jliraper@uaslp.mx

]]> 3 Centro de Investigación y Estudios de Posgrado, Facultad de Ingeniería (CIEP) Universidad Autónoma de San Luis Potosí. México. E–mail: vcardena@uaslp.mx4 Centro de Investigación y Estudios de Posgrado, Facultad de Ingeniería (CIEP) Universidad Autónoma de San Luis Potosí. México. E–mail: ralvarez@uaslp.mx

Recibido: marzo de 2007

Aceptado: marzo de 2008

Resumen

Este trabajo presenta la aplicación de un procesador digital de señales (DSP) para el control de un rectificador PWM trifásico para aplicaciones industriales, al cual se le amplían sus funciones para tener capacidad de compensar caídas de voltaje instantáneas. El estudio resalta las ventajas que ofrece el DSP para controlar el rectificador haciendo uso de la transformación del sistema de un marco de referencia fijo a uno síncrono (teoría D–Q) y controladores clásicos. Se presenta el análisis del sistema, así como resultados de simulación y experimentales para validar la operación del DSP como elemento controlador del sistema.

Descriptores: Calidad de la red eléctrica, distorsión armónica, procesador digital de señales, rectificador PWM trifásico, teoría D–Q, compensación de caídas de voltaje instantáneas.

]]> Abstract

This work presents the application of a digital signal processor (DSP) for the control of a three–phase PWM rectifier for industrial applications, to which are extended their functions to have capacity to compensate voltage sags. The study stands out the advantages that the DSP offers to control, based on the system transformation from fix reference frame to synchronous reference frame (D–Q theory) and classical controllers. The analysis of the system is presented, as well as simulation and experimental results to validate the operation of the DSP as system element controller.

Keywords: Power quality, harmonic distortion, digital signal processor, three–phase PWM rectifier, D–Q theory, sags compensation.

Introducción

La conversión de la corriente alterna (CA) a corriente directa (CD) se realiza mediante circuitos rectificadores. Cuando se requieren bajas potencias estos circuitos suelen ser monofásicos, pero cuando la potencia es elevada se utilizan trifásicos. Tanto los circuitos rectificadores monofásicos como los trifásicos se comportan como cargas no lineales para la red de suministro eléctrico, ya que a un incremento de voltaje no corresponde un incremento proporcional de corriente. Lo anterior, origina que la corriente demandada se encuentre distorsionada, generando así problemas de bajo factor de potencia y distorsión armónica.

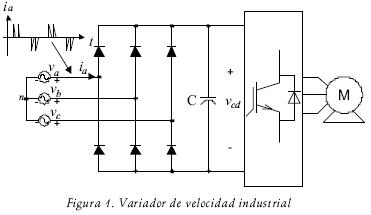

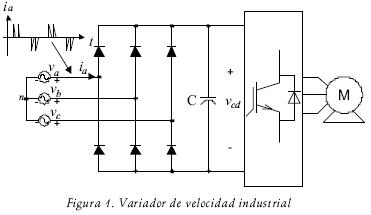

La figura 1 muestra un sistema variador de velocidad industrial, el cual es una aplicación típica de un rectificador trifásico. En dicha figura se muestra la forma de onda que tiene la corriente de la línea. Los picos pueden llegar a un valor que afecte el funcionamiento del sistema y la alta distorsión armónica provoca un factor de potencia bajo, lo cual origina un impacto económico importante.

Otro problema importante es cuando ocurre un sag (disminución instantánea del valor de la tensión de alimentación), el voltaje en la carga disminuye afectando el funcionamiento del sistema. Un estudio muestra que un sag de tensión con una duración de 12 ciclos de red o más y una reducción del 20% en la tensión, es suficiente para activar las protecciones asociadas a un proceso continuo relacionado con motores (Sarmiento, et al., 1996). Las soluciones para reducir la magnitud o el efecto de las corrientes armónicas en una red eléctrica pueden clasificarse en los siguientes grupos:

]]>– Aumentar el número de pulsos de los rectificadores o la configuración de cargas para que éstas se comporten como convertidores con un mayor número de pulsos.

– Utilizar técnicas de inyección de corriente del lado de tensión en CD para así reducir el contenido de corrientes armónicas.

– Emplear rectificadores PWM.

– Emplear filtros pasivos y activos.

Este trabajo presenta el uso de un rectificador PWM trifásico para disminuir los problemas de degradación de la calidad de la red eléctrica originados por la distorsión armónica de un sistema de rectificación (Yimin, et al., 1994), al mismo tiempo, se le amplían sus funciones para compensar los sags de voltaje. Las propiedades de un rectificador PWM trifásico son bien conocidas (Morán, et al., 1992; Stankovic, et al., 2000; Lin, et al., 2004), entre las cuales se encuentran: (1) Compensación del factor de potencia. (2) Cancelación de corrientes armónicas. (3) Capacidad para balancear las corrientes de línea. (4) control del flujo de potencia. (5) Capacidad de regular la alimentación de CD a la carga.

Se presenta el desarrollo de un sistema de control empleando un procesador digital de señales (DSP) como el dispositivo controlador, generando las señales de disparo de los interruptores que llevan a cabo la operación del rectificador PWM trifásico. El DSP debe procesar la información muy rápidamente para poder generar en línea las señales de compensación.

Descripción del sistema

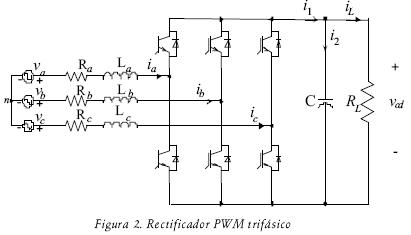

La figura 2 muestra la topología del rectificador PWM trifásico considerado en este trabajo. La, Lb y Lc son bobinas para lograr la corrección del factor de potencia. Ra, Rb y Rc son las resistencias asociadas a dichas bobinas.

]]>

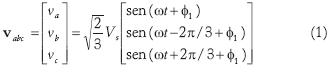

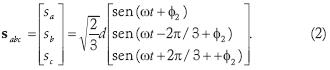

La fuente de alimentación de voltaje trifásica y la función de conmutación de los transistores bipolares de com puerta aislada (IGBT) se pueden expresar como:

Donde la función de conmutación sa se aplica a los IGBT's de la fase " a", sb a los de la "b" y sc a los de la "c", d es el valor del ciclo de trabajo de los interruptores, el cual varia entre 0 y 1. VS es un valor es calado del máximo de la alimentación que corresponde a la componente directa resultante después de aplicar la transformación de coordenadas tratada más adelante. Sin pérdida de generalidad, Φ1 por simplicidad se puede considerar cero y Φ2 tiene un papel importante en el control que se explica posteriormente.

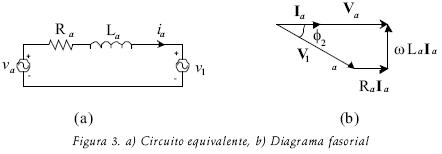

El principio de operación del rectificador PWM consiste en encender y apagar los interruptores siguiendo un patrón de conmutación senoidal, controlando la fase (Φ2) con respecto a la red de alimentación. Si se ignoran las componentes armónicas asociadas al patrón de conmutación, el rectificador puede considerarse como una fuente de voltaje de CA senoidal trifásica. La figura 3(a) muestra el circuito equivalente de la componente fundamental de una sola fase, mientras que la figura 3(b) muestra su diagrama fasorial. Ra representa la resistencia de la bobina y v1 es el voltaje de fase generado por el rectificador. La corriente Ia está dada por:

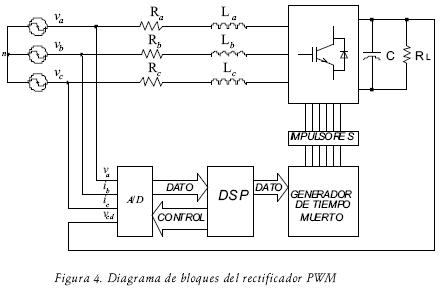

La figura 4 muestra un diagrama de bloques del rectificador PWM trifásico. Se pueden distinguir claramente el sistema de potencia y el de control. La parte fundamental del sistema de control es un procesador digital de señales (DSP), el cual debe llevar a cabo el procesamiento de la información que consiste en lo siguiente:

a) Controlar la operación del convertidor analógico–digital para hacer la medición de las variables.

b) Llevar a cabo el procesamiento de las señales para calcular en tiempo real las condiciones de operación instantáneas del sistema.

c) calcular la ley de control que permita cumplir con los objetivos (corrección del factor de potencia y compensación de sags) del sistema.

d) Considerar protecciones tanto para el sistema como para la red eléctrica.

e) Generar el patrón de conmutación para el sistema de potencia. Los pulsos (uno para cada fase) provenientes del DSP se alimentan a un circuito generador de tiempo muerto, cuyo objetivo es que de cada pulso se obtengan dos, el original y su complemento, incorpo rándoles un tiempo muerto para impedir que los transistores de la misma rama estén encendidos simultáneamente.

Se selecciona una frecuencia de operación de 10 kHz, ya que ésta es menor que la frecuencia máxima de conmutación de los interruptores (20 kHz), y ofrece una buena reproducción digital de las señales en el tiempo.

]]> De acuerdo a lo anterior, el tiempo máximo de retardo debido al procesamiento digital es de 100 µs, y considerando que el sistema trabaja en 60 Hz, se tiene un retraso únicamente de 0.6%. Perturbaciones con una rapidez mayor a 100 µs el sistema no las puede compensar, pero los armónicos críticos y la mayoría de los eventos generados por un sagno caen dentro de este rango.Lo anterior muestra que los requerimientos de procesamiento son grandes y por las características inherentes del sistema es necesario que los pasos anteriores se resuelvan en un tiempo mínimo, de lo contrario, se corre el riesgo de compensar una perturbación con un tiempo de retraso. Entonces, de manera natural un sistema de control digital basado en DSP ofrece la posibilidad de cumplir con los requisitos anteriores y utilizar ventajas adicionales que mejoren el desempeño del sistema de potencia.

Análisis del sistema

En la figura 2 se muestra el circuito del rectificador PWM trifásico. Se asume que todos los elementos del circuito son lineales invariantes en el tiempo (LTI), y que todos los voltajes de los interruptores y la fuente de alimentación son balanceados y en caso de ocurrir un sag, se asume que es simétrico. Los interruptores operan en el modo de conducción continuo (MCC), y el patrón de conmutación puede ser cualquier PWM o control d e seis pulsos, tal que los armónicos de conmutación no sean dominantes.

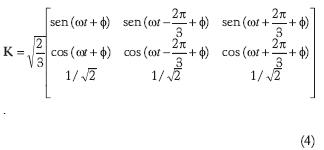

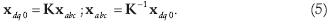

La matriz para la transformación del sistema de un marco de referencia fijo a uno síncrono (transformación D–Q) que mantiene invariantes las potencias, está definida como:

La transformación D–Q y su inversa se definen como:

Si la transformación D–Q se aplica al sistema, el marco de referencia fijo (abc) se transforma en uno giratorio síncrono. La naturaleza variante con el tiempo del sistema se elimina, quedando los voltajes y las corrientes como valores constantes; de esta manera, las ecuaciones del sistema son simples y los controladores pueden ser de bajo orden (Rim, et al., 1988).

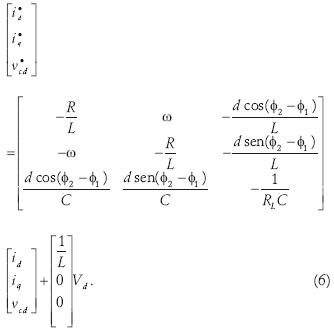

]]> Aplicando la transformación sincronizada con la fase "a" de la alimentación (lo que significa que Φ = Φ1 al sistema rectificador PWM, resulta el circuito mostrado en la figura 5 (Rim, et al., 1990; Rim, et al., 1992). El modelo matemático promedio obtenido a partir del circuito transformado mostrado en la figura 5 está dado por:

Donde R=Ra =Rb =Rc y L=La =Lb =Lc.

La variable id está compuesta por un término de CD, que representa la corriente fundamental asociada con la potencia activa y uno de CA que representa las corrientes armónicas.

Se busca que la componente de CA sea cero, lo que implica que las corrientes de línea en el marco referencial fijo (abc) tengan forma senoidal y estén balanceadas.

La variable iq , asociada a la potencia reactiva, también está compuesta por un término de CD y por uno de CA. Se busca que esta variable sea cero, lo que significa que las corrientes de línea están en fase con sus respectivos voltajes con respecto al neutro.

Cuando se logran las dos condiciones anteriores, el factor de potencia del sistema es unitario.

El voltaje de CD en la carga se puede controlar con las corrientes id e iq, como se puede observar en (6), pero debido a que se desea un factor de potencia unitario iq se busca que sea cero. De esta manera, las variaciones de vcd se controlan solo por id .

]]> El modelo de pequeña señal alrededor del punto de operación es:

Diseño del algoritmo de control

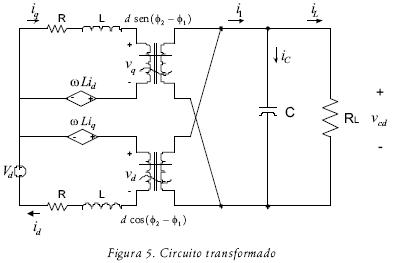

La figura 6 muestra el diagrama de bloques del sistema rectificador PWM trifásico incluyendo la etapa de control. Basados en la cantidad de procesamiento a realizar y tratándose de sistemas cuya respuesta debe ser en tiempo real, de forma natural, se prefiere trabajar con un DSP. En este trabajo ha sido seleccionado el ADSP2101 de la familia de Analog Devices, el cual presenta características que cumplen con los requerimientos del sistema.

El algoritmo de control, basado en la teoría D–Q, es implementado en un sistema mínimo basado en un DSP, el cual aparece como un bloque punteado en la figura 6. El bloque CAD representa el convertidor analógico–digital, el bloque PSD representa el puerto de salidas digitales y el bloque GTM el generador de tiempo muerto.Para llevar a cabo el control del rectificador, deben ejecutarse en línea varios algoritmos que permitan desarrollar tal función.

A continuación, mediante una descripción, se da a conocer la complejidad de cada etapa de procesamiento, así como sus implicaciones en el proceso de control; verificando con resultados experimentales la pertinencia de usar un DSP como plataforma de control.

Los algoritmos que se deben ejecutar están referidos a la etapa de control de la figura 6.

]]>A) Cálculo de las señales de retroalimentación

Para calcular las señales de retroalimentación se necesita contar con un algoritmo que sea capaz de detectar en tiempo real las condiciones de operación del sistema, hacer la transformación de un marco referencial fijo a uno giratorio síncrono y por último acondicionar las señales para poderlas alimentar al sistema de control. El proceso de cálculo de las señales es como sigue:

1. Un convertidor analógico digital convierte las señales de interés. Son 8 canales multiplexados y el tiempo de conversión total de los 8 canales es de 21.2 µS. Se ha ce la medición de 5 señales.

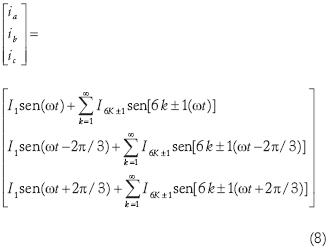

2. Ajustar las escalas de las señales provenientes de los convertidores de analógico a digital, tomando en cuenta las ganancias de los sensores. La corriente trifásica con componen tes armónicas se puede escribir como:

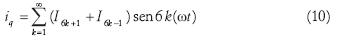

3. Se efectúa la transformación D–Q de las variables del sistema por medio de la operación descrita en (5). En esta etapa del algoritmo existen partes críticas: Se deben generar una función seno y una coseno internamente. Además, es necesario que estén sincronizadas con la red eléctrica, por lo que se requiere programar un algoritmo digital de sincronía. En caso de no generarse adecuadamente las funciones o que no estén perfectamente sincronizadas, se obtendrá información incorrecta de la transformación. Las salidas de esta etapa son id e iq, las cuales tienen componentes de CD relacionadas con la frecuencia fundamental de las corrientes en el marco referencial fijo (abc) y componentes de CA relacionadas con la presencia de armónicos en las mismas:

4. La siguiente etapa es un filtro digital pasa altas. Tiene la función de dejar pasar aquella parte de la corriente id relacionada con los armónicos presentes en las corrientes de línea. E sta etapa del proceso es crítica. El filtro deberá sintonizarse de tal forma que no introduzca desfasamientos en las señales alternas ni atenuaciones.

]]> 5. En este trabajo se utilizó un filtro Butterworth de segundo orden con una frecuencia de corte de 16 Hz. La iq no se filtra por que se desea que toda esta corriente sea igual a cero.B) Cálculo de la ley de control

En esta etapa existe amplia libertad para escoger una función de control; sin embargo, la idea principal es considerar aquella ley de control que aporte un mejor desempeño al sistema físico. Basados en el modelo de pequeña señal del rectificador PWM y para comprobar que el sistema funciona, se seleccionan controladores PI que bastan para asegurar que las variables del sistema puedan seguir a una referencia (Zargari, et al., 1995). También puede resultar muy atractivo desde un punto de vista de desempeño, considerar algoritmos de control no lineal tales como pasividad o modos deslizantes. Esta clase de algoritmos de control requiere de un estudio aparte por su complejidad.

C) Cálculo de las señales de compensación

Para realizar el cálculo de las señales de compensación, se llevan a cabo las siguientes operaciones:

1. Primero se efectúa la transformación D–Q inversa para obtener, a partir de las señales de referencia en el marco giratorio síncrono, id* e iq *, las señales de compensación en el marco referencial fijo, ia*, ib* e ic*. Nuevamente, esta parte es numéricamente impor tante ya que se requie re resolver la inversa de una matriz, cuyos valores son variables en el tiempo.

2. Finalmente, se generan los patrones de conmutación mediante un modulador senoidal del ancho de pulsos (SPWM) implementado internamente en el DSP. Las señales de compensación, que se pueden considerar unas funciones "continuas", se traducen a ciclos de trabajo de encendido y apagado para los interruptores de potencia. Una forma simple de lograrlo es mediante la comparación de dichas señales de compensación con una función triangular generada internamente en el DSP.

Todo el procesamiento del algoritmo de control se efectúa en aproximadamente 60 µs, por lo que comparado con la frecuencia de operación del rectificador (60 Hz), se puede considerar que el controlador basado en el DSP opera en tiempo real.

]]>Resultados de simulación y experimentales

Se construyó un prototipo basado en el esquema mos trado en la figura 6 para validar el análisis y verificar la operación del DSP como controlador en tiempo real para el rectificador PWM trifásico. Adicionalmente, se simuló su operación en MATLAB SIMULINK. Las características físicas del prototipo son las siguientes:

• Potencia de salida: 2.48 kW.

• Tipo de alimentación: Trifásica, 63.5 ± 10 % Vrms línea a neutro, 60 Hz.

• Voltaje de CD en la carga: 200 V.

• Ra, Rb y Rc: 1.08 Ω.

• La, Lb y Lc: 5.25 mH.

• Capacitor de filtrado (C): 2400 µF.

]]> • RL: 16.13 Ω• Ganancia proporcional de los controladores: 1.

• Ganancia integral controlador corriente d: 500

• Ganancia integral controlador corriente q: 500

• Ganancia integral controlador de voltaje: 450.

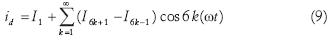

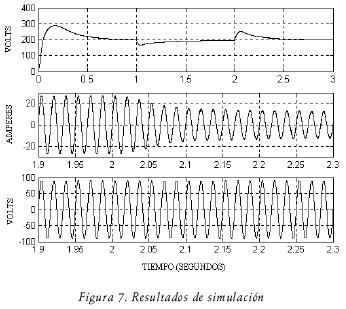

La figura 7 muestra los resultados de simulación con conmutaciones del rectificador PWM sujeto a un cambio de carga tipo escalón del 100% al 50%. El trazo superior corresponde al voltaje de CD de la carga, el trazo intermedio es un detalle de la corriente de línea d e la fase a y el trazo inferior es el voltaje de la fase a con respecto del neutro.

Se observa que el voltaje en la carga se mantiene regulado ante cambios de carga y que la corriente de línea es senoidal y en fase con el voltaje, lo que significa que el factor de potencia es unitario.

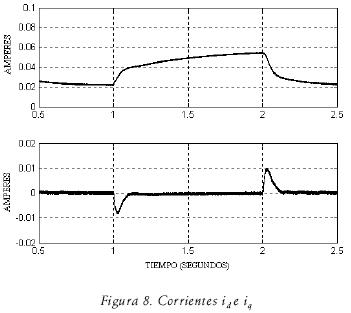

La figura 8 muestra las corrientes, id (trazo superior) e iq (trazo inferior) de simulación.

]]>

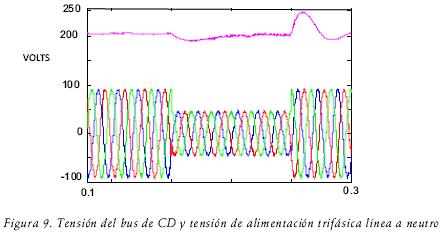

La figura 9 muestra una simula ción de un sag trifásico simétrico y el efecto de la compensación del rectificador trifásico en el lado de CD.

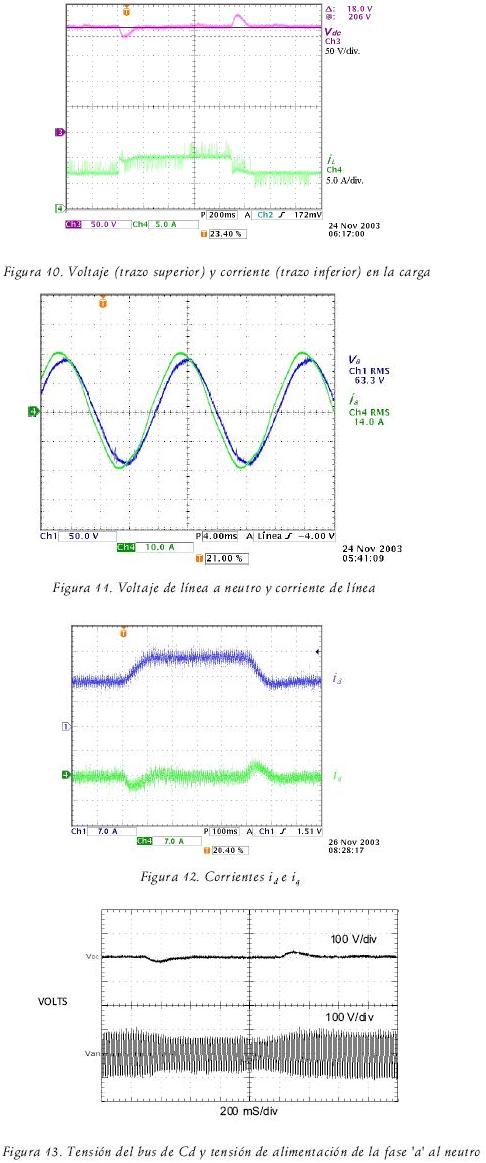

De la figura 10 a la 13 se muestran los resultados experimentales obtenidos con el prototipo construido en el laboratorio. La figura 10 muestra el voltaje y la corriente en la carga cuando ocurre un cambio de carga tipo escalón. Nótese que aún cuando la corriente varía, el voltaje se mantiene constante.

La figura 11 muestra el voltaje de línea a neutro y la corriente de línea. El factor de potencia es cerca no a la unidad.

La figura 12 muestra las corrientes, id (trazo superior) e iq (trazo inferior) medidas experimentalmente. Nótese la similitud de con la figura 8 obtenida por simulación.

]]> La figura 13 muestra la respuesta del rectificador PWM ante un sag de voltaje simétrico. La gráfica superior corresponde al voltaje de CD en la carga, mientras que el inferior muestra la fase a de la alimentación al momento del sag. Note que la tensión en la carga se mantiene regulada, aún en la presencia del sag (en este caso, la alimentación cae a un 30% de su valor nominal).

Conclusiones

En este artículo se presenta un análisis del rectificador PWM, el cual incluye el modelado matemático promedio y de pequeña señal, basados en la transformación de un marco referencial fijo (abc) a uno giratorio síncrono (dq0). A partir de estos modelos, es posible concluir que haciendo uso de la transforma da D–Q las funciones del rectificador PWM pueden ampliarse para compensar sags de voltaje simétricos, además de corregir el factor de potencia.

Se hace una descripción de cada etapa del sistema de control implementado en un sistema digital basado en un DSP, destacando los puntos críticos. Se demuestran mediante simulaciones y resultados experimentales las funciones originales (corrección del factor de potencia) y las amplia das (compensación de sags) para un sistema con capacidad de 2.48 kW. Lo anterior puede tener aplicaciones en sistemas críticos donde estén involucrados variadores de velocidad para motores de inducción.

Agradecimientos

Los autores desean agradecer el soporte financiero de los siguientes patrocinadores: Consejo Nacional de Ciencia y Tecnología (CONACyT) con los proyectos J37670–A y C01–45920/A–1 y a la Universidad Autónoma de San Luis Potosí–Fondo de Apoyo a la Investigación con el proyecto C07–FAI–04–10.12.

Referencias

]]>Lin B.R., Y.C. Lee. Analysis and Implementation of a Three–Phase Four–Wire Switching Mode Rectifier Based on a Switch–Clamped Scheme. IEE Proc.–Electr. Power Appl., 151(3). 2004. [ Links ]

Morán L., Ziogas P., Ojos G. Design Aspects of Synchronous PWM Rectifier–Inverter Systems Under Unbalanced Input Voltage Conditions. IEEE, Transactions on Industry Applications, 28(6). 1992. [ Links ]

Rim C.T, Hub D.Y., Cho G.H. The Graphical D–Q Transformation of General Power Switching Converters. IEREE IAS Conf. Rec., 940–945. 1988. [ Links ]

Rim C.T., Hu D.Y., Cho G.H. Transformers as Equivalent for Switches: General Proofs and D–Q Transformation–Based Analyses. IEEE Transactions on Industry Applications, 26(4):777–785. 1990. [ Links ]

Rim C.T., Choi N.S., Cho G.C. A Complete DC and AC Analysis of Three Phase Current Source PWM Rectifier Using Circuit D–Q Transformation. IEEE Transactions on Industry Applications, 489–495. 1992. [ Links ]

Sarmiento H.G., Estrada E. A Voltage Sag Study in an Industry with Adjustable Speed Drives. IEEE industry Applications Magazine. 1996. [ Links ]

Stankovic A.V., Lipo T.A. A Novel Control Method for Input Output Harmonic Elimination of the PWM Boost Type Rectifier Under Unbal anced Operating Conditions. On: Applied Power Electronics Conference and exposition, APEC–2000. [ Links ]

Yimin J., Hengchun M., Lee F.C., Borojevic D. Simple High Performance Three–Phase Boost Rectifiers. On: Power Electronics Specialists Conference, PESC '94 Record (25th, Annual IEEE, 1994). Vol. 2, pp. 1158–1163. [ Links ]

Zargari N.R., Joós G. Performance Investigation of a Current–Controlled Voltage Regulated PWM Rectifier in Rotating and Stationary Frames. IEEE Transactions on Industrial Electronics, 42(4):396–401. 1995. [ Links ]

]]> Semblanza de los autores

Ciro Núñez–Gutiérrez. Recibió los grados de maestro y doctor en ciencias por el Centro Nacional de Investigación y Desarrollo Tecnológico (CENIDET) en 1997 y 2002, respectivamente. Desde el año 2002, trabaja en la Universidad Autónoma de San Luis Potosí. Sus intereses de investigación incluyen calidad de la red eléctrica, control de motores y electrónica de potencia.

Jesús Lira–Pérez. Recibió el título de ingeniero en electrónica y comunicaciones por el Instituto Tecnológico y de Estudios Superiores de Monterrey en 1978 y el grado de maestría en ingeniería eléctrica por la Universidad Autónoma de San Luis Potosí en 2004. Ha sido profesor investigador en la misma institución desde 1987 y actualmente realiza sus estudios para obtener el grado de doctor en ingeniería eléctrica. Sus intereses de investigación son la corrección del factor de potencia, la electrónica de potencia y la calidad de la energía eléctrica.

Víctor Manuel Cárdenas–Galindo. Recibió el grado de ingeniero en electrónica de la Universidad Autónoma de San Luis Potosí en 1992. En 1994 y 1999, obtuvo el grado de maestro en ciencias y doctor en ciencias en electrónica de potencia, respectivamente, por parte del Centro Nacional de Investigación y Desarrollo Tecnológico, CENIDET. Desde el año 2000, es profesor investigador en la Universidad Autónoma de San Luis Potosí en donde ha formado un grupo de investigación en calidad de energía eléctrica. Sus líneas de interés son la propagación y compensación de armónicos generados por convertidores estáticos en sistemas industriales, calidad de energía y convertidores DC/AC.

Ricardo Alvarez–Salas. Obtuvo el grado de licenciado en electrónica por la Universidad Autónoma de San Luis Potosí en 1993, asimismo, el grado de maestría en ciencias en electrónica y tele comunicaciones del Centro de Investigación Científica y de Educación Superior de Ensenada, CICESE, en 1996. En 1998 y 2002, recibió el Diploma de Estudios Avanzados (DEA) y el de doctor en control automático, respectivamente, por el Instituto Nacional Politécnico de Grenoble, Francia. Actualmente es profesor investigador de la Facultad de Ingeniería de la Universidad Autónoma de San Luis Potosí. Sus áreas de interés son el control no lineal y el control de máquinas eléctricas y de convertidores estáticos.

]]>