@1kHz y consumo de potencia de 237µW.

@1kHz y consumo de potencia de 237µW.

Maya-Hernández P.M.1, Sanz-Pascual M.T.1, Díaz-Sánchez A.1, Calvo B.2

1 Instituto Nacional de Astrofísica, Óptica y Electrónica. Luis Enrique Erro no.1, Tonantzintla, Puebla, México.

2 Grupo de Diseño Electrónico I3A, University of Zaragoza. Pedro Cerbuna no.9 Zaragoza, España.

Recibido: 8 de febrero de 2013

Aceptado: 2 de junio de 2014

Resumen

Una técnica para la medición de la amplitud de una señal, incluso si el ruido y las interferencias superpuestas son mayores que la propia señal, es la técnica de detección sensible a fase, que es la base de los amplificadores lock-in. En este trabajo se presenta un nuevo diseño de amplificador lock-in en modo corriente, integrado en una tecnología CMOS de 0.18µm con voltaje de alimentación de 1.8V, y que es adecuado para aplicaciones portátiles gracias a su reducido consumo de potencia y voltaje de alimentación único. La arquitectura propuesta es capaz de recuperar una señal de interés de ambientes ruidosos con errores por debajo del 6.1% para una reserva dinámica de 42.7dB, está provista de una ganancia entre 1.2 y 20.3dB programable de forma digital, ruido referido a la entrada de  @1kHz y consumo de potencia de 237µW.

@1kHz y consumo de potencia de 237µW.

Palabras Clave: Diseño Analógico CMOS; Circuitos de Acondicionamiento de Sensores; Amplificadores Lock-In; Recuperación de señales; Detección Sensible a Fase.

Abstract

A technique for measuring the amplitude of a signal, even if the superimposed noise and interferences are higher than the signal itself, is the technique of phase sensitive detection, which is the basis of lock-in amplifiers. In this work a novel design of an integrated current mode lock-in amplifier in 0.18μm CMOS technology with 1.8V supply voltage is presented. It is suitable for portable applications thanks to its reduced low power consumption and single supply voltage. The proposed architecture is capable of recovering a signal of interest from noisy environments with errors below 6.1% for a dynamic reserve of 42.7dB. It is provided of a digitally programmable gain ranging from 1.2 to 20.3dB, the input referred noise is  @1kHz and power consumption is 237μW.

@1kHz and power consumption is 237μW.

Keywords: CMOS Analog Design; Sensor Conditioning Circuit; Lock-In Amplifier; Signal Recovery; Phase-Sensitive Detection.

1. Introducción

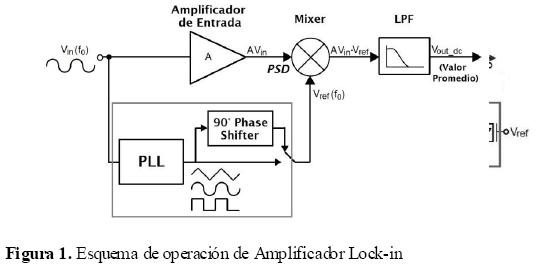

]]> La utilización de sensores y actuadores se ha vuelto indispensable en nuestra vida cotidiana debido a la capacidad que ofrecen para el monitoreo y control de diversas magnitudes físicas y químicas, favoreciendo el desarrollo de una amplia gama de aplicaciones en ramas científicas, médicas, industriales, etc[1,2]. Sin embargo, la detección de la señal puede convertirse en un reto debido a que normalmente su nivel de voltaje es bajo, y puede verse ensombrecida por ambientes ruidosos que superen incluso en amplitud a la señal de interés[3]. Es por ello que surge la necesidad de utilizar técnicas de amplificación especiales que incrementen la relación señal-ruido (SNR) de estos sistemas. Una técnica que permite realizar la medición de la amplitud incluso si el ruido y las interferencias superpuestas son mayores que la propia señal, es la técnica de detección sensible a fase (PSD, por sus siglas en inglés), en la cual basan su modo de operación los amplificadores lock-in (LIAs) [4].Un LIA es un sistema que reduce el ancho de banda del ruido mediante una detección síncrona. En la Figura 1 se observa el esquema de operación de un amplificador lock-in. La señal de entrada Vin es una senoidal de frecuencia f0. Esta señal es amplificada por un amplificador de instrumentación de ganancia A. Mediante un circuito PLL se genera una señal de referencia Vref a la misma frecuencia f0, con forma senoidal, triangular o cuadrada dependiendo de la aplicación. Ambas señales se multiplican, pudiendo expresase el producto como una serie de armónicos. Finalmente, la señal resultante es enviada a un filtro pasa bajas (LPF) que elimina las componentes armónicas AC y permite extraer una contribución en DC (Vout_dc) proporcional a la señal de interés [4, 5]. Para una señal de referencia cuadrada, el nivel de DC obtenido viene dado por:

De la ecuación anterior se puede determinar que la respuesta del sistema dependerá del desfase que exista entre la señal de interés y la señal de referencia, el valor θ. Si Vin y Vref se encuentran en fase (θ=0°), la señal de interés es completamente rectificada y la componente en DC es máxima y proporcional a la amplitud de la señal de entrada.

Cuando el desfase es θ=90° o θ=270°, la contribución en DC es nula, por lo que la salida es igual a tierra (Vdd/2 si el sistema se alimenta con una sola fuente Vdd) y no es posible determinar el valor de la señal de interés. En casos intermedios, la salida toma valores intermedios, por lo que es conveniente que las señales de entrada y de referencia se encuentren en fase, para obtener la máxima contribución en DC y así optimizar la recuperación de la señal.

Como señal de referencia (Vref) se utiliza normalmente una señal cuadrada, ya que es más fácil de generar que otro tipo de funciones, su amplitud puede mantenerse más estable y el cruce por cero está mejor definido [6]. Además, la multiplicación de la señal de entrada por la señal cuadrada es equivalente a tener 2 fases de operación, una en la que se deja pasar la señal y otra en la que no; esto se puede implementar simplemente mediante interruptores, mientras que una señal senoidal o triangular requiere de circuitos más complejos para su generación. Finalmente, otra ventaja al utilizar esta forma de onda, es que se tiene una mayor sensibilidad en todo el sistema frente al uso de señales de referencia senoidales o triangulares.

Los amplificadores lock-in se utilizan ampliamente en la detección de señales ópticas [7, 8] ya que evitan la deriva térmica y errores de detección de luz no deseada, inconvenientes presentes en otras técnicas basadas en acoplamiento en DC a la entrada. Además, los LIAs también se utilizan para la detección de bajas concentraciones de gas, ya sea mediante la medición de impedancias (resistencia y capacitancia) con detectores de doble fase [9] o mediante la detección del nivel de DC que responde a los pequeños cambios producidos por variaciones en la concentración de gas [10]. Asimismo, en estructuras resonantes excitadas magnéticamente se pueden detectar señales de muy baja amplitud sumergidas en niveles de ruido en base a la activación de una frecuencia determinada mediante una bobina [11].

En la literatura se encuentran pocas implementaciones integradas de LIAs[7-15]. Algunas operan en modo de alimentación dual [12,13], y la mayoría presenta un consumo de potencia que va de las unidades a las centenas de mW [7-13], por lo que no son adecuadas para sistemas portátiles que operan con baterías. En este trabajo se presenta una implementación alternativa de un LIA analógico en modo corriente, con consumo reducido de potencia del orden de µW, para su utilización en aplicaciones portátiles. El circuito se basa en la técnica de detección síncrona en modo corriente utilizada en [14, 15]. Sin embargo, en este caso se elimina el bloque de entrada, realizándose la conversión de la señal directamente en un circuito multiplicador altamente lineal, lo que permite tener una reducción del área y el consumo de potencia. Además, mediante el uso de un amplificador de transimpedancia (TIA) con un amplio rango dinámico se logra mejorar el rango de procesamiento de señal del circuito. Como resultado el sistema es más compacto, lineal y con mayor rango dinámico, aumentando la versatilidad para su uso en distintas aplicaciones portátiles.

]]> El trabajo se encuentra desarrollado de la siguiente manera: en la Sección II se presenta el LIA propuesto, así como la topología utilizada para cada uno de los bloques que lo conforman. Todos los circuitos fueron diseñados en una tecnología CMOS de 0.18µm, con un voltaje de alimentación Vdd=1.8V. En la sección III, se presentan los resultados de simulación de la caracterización eléctrica del LIA, así como un resumen del funcionamiento del circuito ante señales indeseadas. Finalmente en la sección IV se presentan las conclusiones.

2. Amplificador Lock-In Propuesto

La arquitectura del LIA propuesto se muestra en la Fig. 2. La etapa de entrada es un circuito multiplicador que realiza la rectificación síncrona en modo corriente de la señal de entrada Vin y la señal de referencia Vref . A continuación, un circuito divisor de corriente brinda programabilidad al circuito al ponderar la corriente de manera binaria. Mediante un amplificador de transimpedancia, la señal es convertida nuevamente a voltaje. Finalmente, un filtro pasa bajas realiza el promediado de la señal de interés y elimina las componentes armónicas de alto orden.

Esta topología presenta ventajas frente a las implementaciones en modo voltaje [7-13], ya que el procesamiento de la señal en el dominio de la corriente ofrece mayor linealidad, un ancho de banda más amplio, rango dinámico mayor y bajo consumo de potencia [16,17]. Frente a las implementaciones previas en modo corriente, propuestas por los autores en [14,15], se obtienen estas mismas ventajas gracias a un diseño optimizado que ha permitido reducir el número de bloques que conforman el LIA, reducir el consumo de potencia y mejorar la linealidad.

2.1. Multiplicador

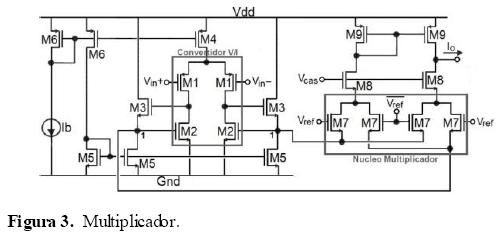

Como bloque de entrada, se utiliza un multiplicador que reduce la distorsión a partir del uso de nodos de baja impedancia y que incorpora en un mismo circuito la función de conversión de la señal de voltaje a corriente y la rectificación síncrona de la señal de entrada [18], como muestra la Fig. 3.

]]>

Su modo de operación es el siguiente: el par diferencial de entrada M1 convierte la señal de entrada en corriente. Los transistores M3 funcionan como seguidores de fuente, fijando el voltaje Vgs de los transistores M2, con lo que la señal se copia a los nodos 1 de baja impedancia. De estos nodos, la señal es enviada a los transistores M7 de cruce acoplados que forman una celda Gilbert. Las señales de referencia Vref y  son inyectadas en las compuertas de estos transistores M7, realizándose la rectificación síncrona de la señal de entrada. Los transistores M8 proveen un nodo de baja impedancia a los drenadores de los transistores M7 de modo que la corriente fluye hacia las cargas activas M9. Así, la corriente resultante I0 está dada por:

son inyectadas en las compuertas de estos transistores M7, realizándose la rectificación síncrona de la señal de entrada. Los transistores M8 proveen un nodo de baja impedancia a los drenadores de los transistores M7 de modo que la corriente fluye hacia las cargas activas M9. Así, la corriente resultante I0 está dada por:

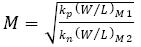

donde  , y kp y kn son los parámetros de transconductancia de los transistores M1 y M2, respectivamente. Cabe destacar que el uso de la técnica de bootstrapping (M2-M3) incrementa la linealidad del circuito.

, y kp y kn son los parámetros de transconductancia de los transistores M1 y M2, respectivamente. Cabe destacar que el uso de la técnica de bootstrapping (M2-M3) incrementa la linealidad del circuito.

Los parámetros más importantes obtenidos de la caracterización del multiplicador de entrada se muestran en la Tabla 1. El circuito presenta una linealidad de –52.9dBa 1kHz para una señal de salida de 10µApp y un consumo de potencia de 120.1µW.

2.2. Divisor de Corriente Programable

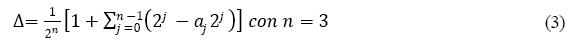

El divisor de corriente programable de 3 bits está basado en un divisor R-2R implementado con transistores PMOS, como se muestra en la Fig. 4, con la finalidad de obtener un circuito compacto, al eliminar el uso de resistores, y que lleve a cabo una división lineal de la corriente [19].

]]>

La corriente de entrada I0 se divide en dos corrientes: Iout=∆I0 y Iout2= (1–∆)I0. El factor de división ∆ se controla mediante una palabra digital Va(3)={a2, a1, a0} y está dado por:

La corriente de salida Iout se conecta a la entrada del siguiente bloque, el amplificador de transimpedancia, mientras que la corriente Iout2 se conecta a Vdd/2 para una división de corriente adecuada. La ventaja de usar transistores paralelos para generar R/2 y un transistor para generar R es que la caída de voltaje entre el nodo de entrada y los nodos de corriente de salida es menor que si fueran 2 transistores en serie para generar 2R y uno para generar R [20].

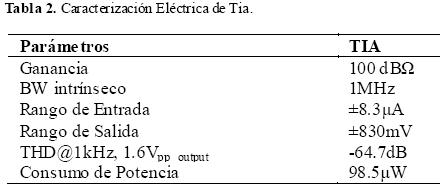

2.3. Amplificador de Transimpedancia

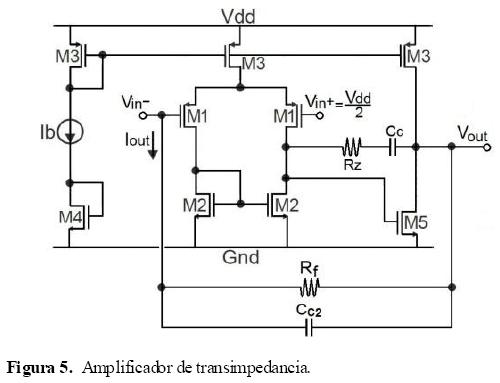

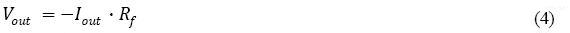

Para la conversión de corriente a voltaje se utilizó el amplificador de transimpedancia (TIA) mostrado en la Fig. 5, que consiste en un amplificador diferencial y un resistor de realimentación Rf=100kΩ.

Para el amplificador se utilizó una topología de dos etapas, la primera conformada por un par diferencial PMOS (M1) de salida única y la segunda por un NMOS en fuente común (M5). Esta topología provee una ganancia elevada y un amplio rango de salida. La compensación en frecuencia del circuito se realiza mediante los capacitores Cc=6pF, Cc2=1.5pF y el resistor Rz=4kΩ, que aseguran la estabilidad del circuito. La salida del circuito viene dada por:

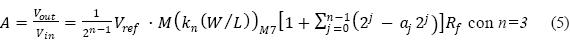

Considerando la conexión en cascada de todos los bloques hasta aquí presentados, la ganancia total del sistema en función de la palabra digital Va(3) está dada por la siguiente expresión:

Un inconveniente de esta configuración es que la ganancia depende de los parámetros de los transistores de la etapa de entrada, por lo que es sensible a variaciones de proceso. Sin embargo, la programabilidad hace posible compensar este efecto en una fase inicial de calibración.

2.4. Filtro Pasa Bajas

Para la implementación del filtro pasa bajas de salida, se utilizó una red pasiva RC de segundo orden, cuya frecuencia de corte es igual a fc=5Hz. Se eligió dicho valor para limitar y eliminar todas las componentes armónicas que se encuentren fuera de su ventana de aceptación, y extraer únicamente la componente en DC. Para su implementación, se utilizaron resistores y capacitores de valor R=6.4MΩ y C=5nF.

Debe observarse que en este trabajo se ha supuesto, por simplicidad, que la señal de entrada al lock-in y la señal de referencia están en fase. No obstante, debido a la gran importancia del la señal de referencia para el funcionamiento correcto del LIA, en implementaciones futuras se generará esta señal mediante un circuito PLL que realice el ajuste de la fase entre las señales Vin y Vref . Para ello, mediante el desplazador de fase se buscará que el circuito entregue una contribución nula de la componente en DC a la salida: esto indicará que las señales se encuentran en un desfase de 90 o 270°, lo que permitirá, mediante un desplazamiento adicional de fase de 90º de la señal de referencia, poner a ambas señales en fase y, con ello, extraer la máxima contribución en DC a la salida.

]]> 3. Resultados de Simulación

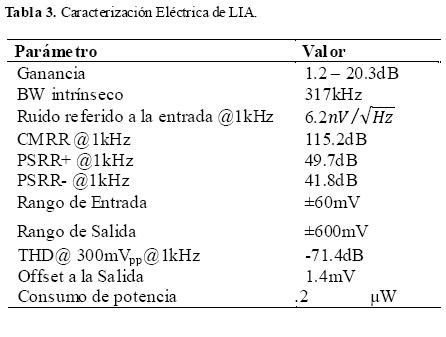

El LIA propuesto fue diseñado en tecnología CMOS de 0.18µm con voltaje de polarización de 1.8V. La caracterización eléctrica obtenida mediante simulación es reportada en la Tabla 3. Cabe destacar que el circuito presenta un elevado rechazo al modo común (115.2dB@1kHz), ruido referido a la entrada de 6.2 nv/ @1kHz y un consumo de potencia de 237.2µW, lo que lo hace adecuado para su uso en aplicaciones portátiles.

@1kHz y un consumo de potencia de 237.2µW, lo que lo hace adecuado para su uso en aplicaciones portátiles.

La Fig. 6 muestra la programabilidad de la ganancia desde el circuito transconductor hasta el amplificador de transimpedancia, con un ancho de banda (BW) de 317kHz, en función de la palabra digital Va(3). Esta ganancia variable brinda flexibilidad al LIA para la detección de señales en distintos rangos; además, dado que el BW del LIA es del orden de centenares de kHz, el campo de aplicaciones se abre a distintos sensores con frecuencias de operación de hasta decenas de kHz, frente a otras implementaciones que trabajan a frecuencia fija y por lo tanto quedan limitados a una única aplicación.

En la Figura 7 se muestra el voltaje Vout a la salida del TIA frente a la señal de entrada Vin para la ganancia máxima y la ganancia mínima.

La capacidad de recuperación de señal del LIA propuesto se puso después a prueba. Para ello, se aplicó una señal senoidal de entrada Vin=0.8mVpp@1kHz al circuito operando a la máxima ganancia. La primera prueba consistió en sumar a la señal Vin una señal de interferencia con amplitud variable y frecuencia de operación fija igual a 10kHz. A continuación, se sumó una señal de interferencia con voltaje Vno=30mVpp y frecuencia de operación variable cercana a la de referencia. Finalmente, se sumó una señal de ruido blanco gaussiano de diferentes valores rms. El voltaje de salida ideal obtenido a partir de la ecuación (1), Vout_dc_id, y el voltaje de simulación, Vout_dc_sim, se reportan en la Tabla 4.

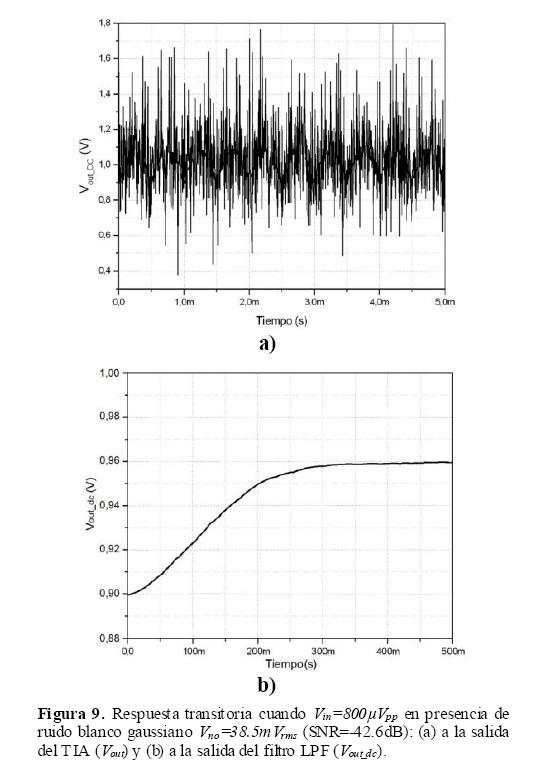

En la Figura 9 se observa la señal de salida del amplificador de transimpedancia y del filtro de salida LPF para el caso de ruido blanco Vno=38.5mVrms. Se observa en la Fig.9(a) que el LIA rectifica la señal de interés, a la cual se superpone la señal de ruido. En la Figura 9(b), se observa cómo el filtro de salida elimina las componentes armónicas de mayor orden, correspondientes al ruido; sin embargo, debido a que algunas componentes frecuenciales de ruido se encuentran muy cercanas a la ventana de aceptación del filtro, el nivel en DC a la salida es mayor que el esperado, obteniéndose un error relativo de 6.1% con respecto al valor ideal. La reserva dinámica (DR) es el parámetro más importante y que mejor representa la capacidad de recuperación de señales sumergidas en ruido de un amplificador lock-in. Concretamente, indica la máxima cantidad de ruido a escala completa que tolera el LIA, expresada en dB [4]; en otras palabras, es la inversa de la peor SNR que puede haber a la entrada del LIA para obtener una señal de salida full-scale sin que el amplificador se sature. En la Fig. 10(a) se observa el error relativo del LIA ante diferentes valores de DR, considerando una señal de interferencia senoidal de frecuencia de 10kHz. Puede observarse que el error aumenta conforme se incrementa la amplitud de la señal de interferencia, obteniéndose un error relativo ε=5.4% para la máxima reserva dinámica DR=42.7dB. En la Fig. 10b se muestra el error relativo en las mediciones del LIA en función de la frecuencia de una señal de interferencia senoidal Vno=30mVpp. Se observa que cuando la frecuencia de la señal de interferencia se acerca a la frecuencia de referencia, la interferencia contribuye en mayor medida al nivel en DC a la salida, como es de esperar, ya que la componente fundamental de estas señales indeseadas pasa por la ventana de aceptación del filtro de salida. Además, se puede observar en la Figura 10(b) que aquellas señales de interferencia cuya frecuencia es submúltiplo de la frecuencia de referencia, en este caso fVno=500Hz, también incrementan el error en el proceso de recuperación, ya que el segundo armónico generado por distorsión armónica coincide con la frecuencia de la señal de referencia, contribuyendo al nivel de DC de la salida e incrementando el error.

Finalmente, se observa en la Tabla4 que las señales de ruido blanco contribuyen en mayor medida al nivel en DC que extrae el filtro de salida, debido a que este tipo de ruido consta de componentes armónicas en todo el rango de frecuencias, por lo que las más cercanas a la frecuencia de referencia pasan por la ventana de aceptación del LPF. A pesar de ello, el circuito LIA propuesto es capaz de recuperar la señal de interés con un error relativo inferior al 6.1% para DR=42.7dB.

]]> Para concluir, se presenta en la Tabla 5 una comparación del funcionamiento del LIA propuesto con otras implementaciones integradas encontradas en la literatura. Los trabajos [8], [12] y [13] cuentan con ganancias elevadas que les permiten detectar señales muy pequeñas; sin embargo, son susceptibles de saturarse si las señales de ruido son elevadas. Por otra parte, un rango de entrada muy pequeño limita a estos circuitos a su uso en aplicaciones específicas. Los trabajos [14] y [15] tienen rangos de entrada mayores, superados por el LIA propuesto al contar con un rango de entrada hasta un orden de magnitud mayor. En cuanto a la linealidad, también el circuito propuesto resulta ser superior a las propuestas anteriores [14] y [15]. Con respecto a la capacidad de recuperación de señales, sobresale el trabajo [12], que alcanza una DR=50dB, aunque no se especifica el error cometido al recuperar la señal. Además, dicho LIA opera con polarización dual de ±2.5V, lo que lo hace inadecuado para su utilización en sistemas portátiles. Finalmente, se observa que el circuito propuesto presenta una reducción en el consumo de potencia con respecto a otros LIAs [8,9,12,13] en al menos un orden de magnitud, mejorando incluso el consumo que presentan los trabajos [14,15], lo que reafirma su idoneidad para aplicaciones portátiles.

4. Conclusiones

En este trabajo se presentó el diseño de un amplificador lock-in en modo corriente en tecnología CMOS 0.18µm, que resulta idóneo para su uso en sistemas portátiles debido a su diseño compacto y su bajo consumo de potencia, de tan solo 237.2µW. La arquitectura propuesta es capaz de recuperar señales de interés de ambientes ruidosos con un error relativo menor al 6.1% tanto para señales de interferencia operando a frecuencias cercanas a la frecuencia de referencia como para señales de ruido blanco, con una reserva dinámica de 42.7dB. El circuito propuesto presenta, además de bajo consumo, un amplio rango de entrada, alta linealidad y programabilidad de la ganancia, lo que le brinda flexibilidad para su utilización en diferentes aplicaciones. Así mismo, ya que el LIA no requiere operar a una frecuencia fija y cuenta con un ancho de banda del orden de centenas de kHz, añade la posibilidad de operación a diferentes frecuencias y, por lo tanto, de aplicación a diferentes tipos de sensores.

Agradecimientos

Se agradece el apoyo otorgado por CONACYT para este trabajo a través de la Beca de Doctorado 235415 y del Proyecto de Investigación CB-SEP-2008-01-99901.

Referencias

[1] G.C.M. Meijer, "Smart Sensor Systems"(Wiley, 2008). [ Links ]

[2] R. Pallás Areny, "Sensores y acondicionadores de señal", 4ta edición (Marcombo, Barcelona, 2003). [ Links ]

[3] T. H. Wilmshurst, "Signal Recovery from Noise in Electronic Instrumentation", 2da edición (Taylor & Francis Group, 1990). [ Links ]

[4] About Lock-in amplifiers, Appl. Note #3, SRS (Stanford Research Systems). http://www.thinksrs.com/downloads/PDFs/ApplicationNotes/AboutLIAs.pdf [ Links ]

[5] C. Falconi, Sensors and Actuators B: Chemical, 121, 295 (2007). [ Links ]

[6] D. P. Blair, P. H. Sydenham, Journal of Physics E: Sci. Instruments, 8, 621 (1975). [ Links ]

]]>[7] G. N. Lu, P. Pittet, G. Sou, G. Carrillo, A. El Mourabit, J. Analog Integrated Circuits and Signal Processing, 37, 57 (2003). [ Links ]

[8] A. Hu,V. P. Chodavarapu, IEEE Transactions on Biomedical Circuits and Systems, 4, 274(2010). [ Links ]

[9] J. Xu, G. Meynants, P. Merken, "Low-Power Lock-In Amplifier for Complex Impedance Measurement", Workshop on Advances in Sensors and Interfaces, pp. 110-114 (2009). [ Links ]

[10] A. De Marcellis, G. Ferri, M. Patrizi, V. Stornelli, A. D'Amico, C. Di Natale, E. Martinelli, A, Alimelli, R. Paolesse, "An integrated analog lock-in amplifier for low-voltage low-frequency sensor interface," IEEE Workshop on Advances in Sensors and Interfaces, pp. 1-5 (2007). [ Links ]

[11] C. Azzolini, A. Magnanini, M. Tonelli, G. Chiorboli, C. Morandi, "Integrated lock-in amplifier for contactless interface to magnetically stimulated mechanical resonators", Proc. Intl. Design and Technology of Integrated Systems Nanoscale (Era,2008). [ Links ]

]]>[12] A. Gnudi, L Colalongo, G. Baccarani, "Integrated Lock-In Amplifier for Sensor Aplications", IEEE Solid State Circuits Conference, pp. 58-61 (1999). [ Links ]

[13] A. D'Amico, A. De Marcellis, C. Di Carlo, C. Di Natale, G. Ferri, E. Martinelli, R. Paolesse, V. Stornelli, Sensors and Actuators, 44, 400(2010). [ Links ]

[14] P. M. Maya Hernández, M. T. Sanz Pascual, B. Calvo, "A 1.8V-0.18µm CMOS Lock-In Amplifier for Portable Applications", IEEE International Symposium on Circuits And Systems, pp. 668-671(2012). [ Links ]

[15] P. M. Maya Hernádez, M. T. Sanz Pascual, B. Calvo, D. Antolin, "A CMOS Low-Power Lock-In Amplifier", IEEE Instrumentation and Measurement Technology Conference, pp. 1804-1807(2012). [ Links ]

[16] G. W. Roberts, A. S. Sedra, Electronics Letters, 25, 759(1989). [ Links ]

]]>[17] B. Wilson, IEE Proceedings Circuits, Devices and Systems 137, 63 (1990). [ Links ]

[18] A. Díaz-Sanchez, J. Ramírez-Angulo, E. Sánchez-Sinencio, G. Han, Analog Integrated Circuits and Signal Processing 19, 163(1999). [ Links ]

[19] K. Bult, G. Geelen, IEEE J. Solid-State Circuits 27, 1730(1992). [ Links ]

[20] M. Pastre, M. Kayal, Methodology for the Digital Calibration of Analog Circuits and Systems with Case Studies (Springer, 2006). [ Links ]

]]>