Introducción

Actualmente los inversores multinivel se utilizan ampliamente en el sector industrial, en aplicaciones de mediano voltaje (2.3 kV a 13.8 kV) y alta potencia (0.4 MW a 40 MW). La característica principal de los inversores multinivel es la capacidad de reducir el voltaje que deben soportar los Dispositivos Semiconductores de Potencia (DSeP), gracias a que se emplean varias fuentes de alimentación en el bus de CD. Otras ventajas que ofrecen los inversores multinivel son: mayor número de niveles en el voltaje de salida, menor contenido armónico, reducción en los transitorios dv/dt y menores pérdidas por conmutación (Palanivel & Dash, 2011; Rodriguez et al., 2002).

Para el diseño de un inversor multinivel se deben considerar dos aspectos importantes: por un lado, se encuentra la topología a emplear que consiste básicamente en la forma en que se colocan los interruptores de potencia y otros componentes físicos, como capacitores, carga, etcétera. Por otro lado, está la forma en que los interruptores son accionados (encendido y apagado).

En cuanto a la topología, los inversores multinivel más utilizados en la industria son: diodos de enclavamiento, conexión en cascada y condensadores flotantes (Rodriguez et al., 2002). En aplicaciones que demandan muy alta potencia (hasta 31 MW), los inversores multinivel en cascada ofrecen grandes ventajas respecto a las otras topologías, debido a su diseño modular y capacidad de expansión en serie (Gordillo, 2011).

Otra de las etapas más importantes en el diseño de los inversores multinivel es la forma en que los DSeP son accionados, debido a que una selección adecuada de la secuencia de conmutación de estos elementos permite obtener voltajes de salida con formas de onda multinivel. Mientras mayor sea el número de niveles, se tendrá una señal con menor distorsión armónica (THD, por sus siglas en inglés Total Harmonic Distortion) (Naderi & Rahmati, 2008).

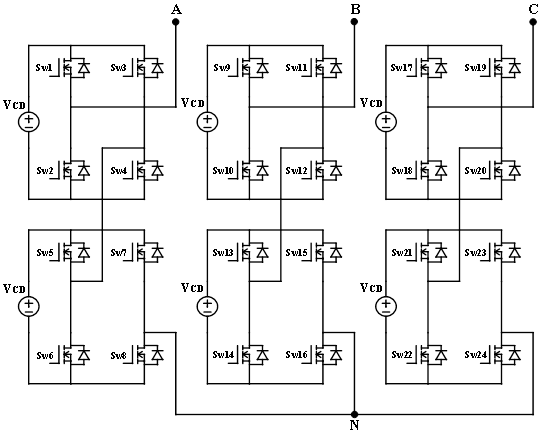

En los inversores multinivel el número de niveles en el voltaje de salida está asociado con el número de DSeP de los que está compuesto el inversor. Para obtener un mayor número de niveles es necesario utilizar un mayor número de DSeP. Por ejemplo, para un inversor en cascada trifásico de cinco niveles por fase, en el voltaje a la salida se requieren de dos módulos de cuatro DSeP, de esta manera con dos módulos y dado que los módulos se encuentran conectados en serie, es posible obtener cinco niveles diferentes de voltaje (+2VCD, +VCD, 0, -VCD y -2VCD), la Figura 1 muestra el diagrama eléctrico asociado a un inversor de cinco niveles.

Con el fin de obtener más niveles y menor THD en el voltaje de salida, es necesario generar un gran número de señales de conmutación para todos los DSeP que integran el inversor. Una forma interesante para obtener estas señales con bastante precisión, es utilizar un arreglo de compuertas programables en campo (FPGA, por sus siglas en inglés Field-Programmable Gate Array) (Rajendra et al., 2009).

El uso de los dispositivos FPGA se ha incrementado en los últimos años, principalmente en la etapa digital de los inversores multinivel, debido a que dispone de múltiples salidas, es fácil de programar, ejecuta las tareas en un tiempo reducido y, sobre todo, por su capacidad de ejecutar tareas de manera paralela (Lakka et al., 2013).

En este artículo se presenta una metodología para generar las señales PWM para un inversor multinivel utilizando un dispositivo FPGA. El resto del documento está organizado de la siguiente manera: en la siguiente sección se describe el principio de funcionamiento del inversor multinivel en cascada. La tercera sección analiza la técnica de modulación implementada en el FPGA. Posteriormente, la sección cuatro explica el procedimiento desarrollado para obtener las señales PWM con un FPGA. Los resultados obtenidos mediante simulación e implementación se presentan en la sección cinco. Finalmente se muestran las conclusiones

Inversor multinivel en cascada

Los inversores multinivel en cascada (CMLI, por sus siglas en inglés Cascaded Multilevel Inverter), están compuestos por dos o más inversores puente completo monofásico conectados en serie, cuya función es generar voltajes con formas de onda escalonadas. En la Figura 1, se muestra el diagrama esquemático de un inversor multinivel en cascada trifásico de cinco niveles utilizando dos puentes completos por fase.

Las características principales de estos inversores son: la capacidad de operar con altos voltajes, reducción del voltaje en modo común, diseño modular, flexibilidad para incrementar el número de niveles sin complicar la etapa de potencia, menores niveles de dv/dt, voltaje de salida casi senoidal (dependiendo del número de niveles), entre otros (Gordillo, 2011; Sanabria, 2004). El voltaje a la salida del inversor medido entre fase y neutro se determina sumando los voltajes individuales que proporciona cada inversor puente completo, tal como se muestra en la ecuación 1 (Sanabria, 2004).

Donde:

V AN = Voltaje de la fase A al neutro (Volts, V)

V CD = Voltaje del bus de CD (Volts, V)

S = Número de fuentes de CD por fase

Para determinar el número de niveles en el voltaje de salida que se obtienen con esta topología, es necesario conocer el número de fuentes de CD que integran el inversor, tal como se muestra en la ecuación 2 (Sanabria, 2004).

Donde:

N = Número de niveles en el voltaje de salida

S = Número de fuentes de CD

La generación de los diferentes niveles en el voltaje de salida depende de una adecuada selección en la secuencia de conmutación de los interruptores de potencia. En la Tabla 1 se muestran seis estados de conmutación posibles, para obtener una forma de onda de cinco niveles (medida de fase a neutro).

Tabla 1: Estados de conmutación de un inversor en cascada de cinco niveles

| Estado | Función de conmutación | |||||||

|---|---|---|---|---|---|---|---|---|

| Sw1 | Sw2 | Sw3 | Sw4 | Sw5 | Sw6 | Sw7 | Sw8 | |

| S0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 |

| S1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 |

| S2 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

| S3 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| S4 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| S5 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

Los estados de conmutación S2 y S3 se denominan estados cero, debido a que conectan la carga a una diferencia de potencial igual a cero, utilizando los interruptores inferior y superior de cada rama del inversor. El resto de los estados se denominan estados de conmutación activos; en el caso de los estados S1 y S4, conectan la carga a una diferencia de potencial de +VDC y -VDC, respectivamente. Mientras que con los estados S0 y S5 se obtiene un voltaje de +2VDC o -2VDC en los terminales de la carga, según sea el caso (Rodriguez et al., 2002).

En la Figura 2 se muestran las trayectorias que siguen las corrientes en la carga y la forma de onda del voltaje de salida, con base en los datos que se presentan en la Tabla 1 (Gordillo, 2011). La conmutación de los interruptores permite sumar el voltaje de las fuentes de CD, consiguiendo un alto voltaje en la salida, mientras que el voltaje que soportan los interruptores de potencia es reducido (Gordillo, 2011; Sánchez, 2004).

Figura 2: Inversor multinivel en cascada de cinco niveles: a) trayectoria de las corrientes y b) forma de onda del voltaje de salida

Comúnmente, la secuencia de conmutación que siguen los interruptores de potencia viene impuesta por un proceso de modulación que determina las características de la señal de salida, entre ellas: forma, amplitud, frecuencia y contenido armónico (Malinowski & Stynski, 2007; Palanivel & Dash, 2011). La técnica de modulación más popular y simple para generar ondas senoidales a la salida de un inversor multinivel es la modulación por ancho de pulso (PWM, por sus siglas en inglés Pulse Width Modulation) (Malinowski & Stynski, 2007).

Técnica de modulación PWM con disposición alterna opuesta de fase

En las técnicas de modulación PWM las señales de compuerta para la activación y desactivación de los DSeP, se obtienen comparando la amplitud de una señal de referencia denominada señal moduladora y una o más señales portadoras, en el caso más simple se utilizan una señal senoidal y señales triangulares, respectivamente (Palanivel & Dash, 2011).

Con el fin de reducir la distorsión armónica en los inversores multinivel, se han desarrollado diferentes técnicas de modulación con multiportadoras, la mayoría basadas en la clásica PWM senoidal (SPWM, por sus siglas en inglés Sinusoidal Pulse Width Modulation) con portadoras triangulares. Estos métodos emplean el desplazamiento de la fase de las portadoras, pero si el ángulo es de 0° se le conoce como disposición de fase y si el ángulo es 180° se le conoce como disposición alterna de fase (Rodriguez et al., 2002). En este artículo se utiliza la modulación PWM con disposición de múltiples portadoras triangulares.

La técnica de modulación PWM con disposición de portadoras consiste en comparar un número determinado de señales portadoras, las cuales tienen la misma amplitud respecto a una señal moduladora de referencia. El número de señales portadoras necesarias para generar un determinado número de niveles en el voltaje de salida se calcula mediante la ecuación 3 (Reyes, 2018; Reyes et al., 2020).

Donde:

Sc = Número de señales portadoras necesarias

N = Número de niveles en el voltaje de salida

La técnica de modulación PWM con disposición de portadoras presenta las siguientes tres variantes: disposición de fase (PD, por sus siglas en inglés Phase Disposition), disposición opuesta de fase (POD, por sus siglas en inglés Phase Opposition Disposition) y disposición alterna opuesta de fase (APOD, por sus siglas en inglés Alternate Phase Opposition Disposition), en las cuales únicamente varía la fase de las señales portadoras (Rathore et al., 2015; Reyes, 2018). En este caso, se utiliza la modulación APOD-PWM.

En la técnica de modulación PWM con disposición alterna opuesta de fase, las señales portadoras se encuentran desplazadas un nivel de CD positivo o negativo y desfasadas 180° respecto a la señal portadora adyacente (Reyes, 2018).

La señal moduladora Vm 1 se expresa como se muestra en la ecuación 4. Las señales Vm 2 y Vm 3 se encuentran desfasadas 120° y -120° respectivamente, tomando como referencia Vm 1 .

Donde:

V m1 = Voltaje de la señal de moduladora 1 (Volts, V)

A m = Amplitud de la señal de moduladora (Volts, V)

f m = Frecuencia de la señal de moduladora (Hertz, Hz)

t = Tiempo (segundos, s)

La señal portadora Vc 1 se obtiene a partir de la ecuación 5. Como regla general, el valor de la amplitud de todas las señales portadoras debe ser igual, por lo tanto, A c1 = A c2 = A c . Las demás señales portadoras se encuentran desplazadas un nivel de CD positivo o negativo, según sea el caso. En nuestro caso, que se requieren cinco niveles de voltaje a la salida, son necesarias cuatro señales portadoras.

Donde:

V c1 = Voltaje de la señal de portadora triangular 1 (Volts, V)

A c = Amplitud de la señal de portadora triangular (Volts, V)

f c = Frecuencia de la señal de portadora triangular (Hertz, Hz)

T = Tiempo (segundos, s)

El índice de modulación de amplitud (m) entre la señal moduladora y la señal portadora se expresa como sigue:

La relación de modulación de frecuencia (f) se determina mediante la ecuación 7.

En la Figura 3a se muestran las señales portadoras en color rojo, azul, naranja y verde; así como la señal moduladora de la fase A en color negro. En la Figura 3b se muestran las señales del voltaje de la compuerta para los interruptores Sw1 en color rojo, Sw3 en color azul, Sw5 en color naranja y Sw 7 en color verde, cabe mencionar que los interruptores Sw2, Sw4, Sw6 y Sw8 son complementarios a los interruptores Sw1, Sw3, Sw5 y Sw7, respectivamente. Utilizando la técnica de modulación APOD-PWM con m=0.9 y f=60.

Implementación de la técnica de modulación

Las técnica de modulación descrita en la sección anterior se implementó en una tarjeta FPGA Altera Cyclone II EP2C5T144, cuyas características y bajo costo la hacen una solución ideal para una amplia gama de aplicaciones, en especial, aquellas áreas relacionadas con el procesamiento y generación de señales (Reyes, 2018).

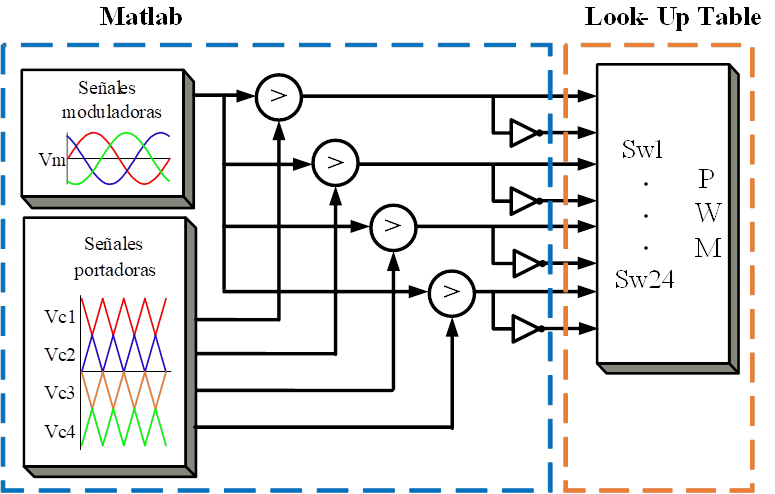

En este caso, el uso del FPGA permite generar los estados de encendido y apagado de los 24 interruptores de potencia que integran el inversor. El procedimiento empleado para generar estas señales se divide en dos programas; un script de Matlab y un código VHDL creado en el software Quartus II.

a) Programación en Matlab

En el programa de Matlab se generan las señales moduladoras y portadoras; tomando en cuenta las ecuaciones presentadas en la sección de la técnica de modulación implementada en el FPGA. Además, en Matlab se comparan todos los valores de la señal moduladora con los valores de la señal portadora durante un ciclo de línea (60 Hz). Si el valor de la señal moduladora es mayor que la señal portadora, la salida del bloque comparador es 1, en caso contrario, la salida es 0. Para tener una buena resolución del bloque comparador, considerando que las señales moduladoras operan a una frecuencia de 3.6 kHz y se tienen 100 puntos para realizar las comparaciones, por lo tanto, el comparador opera a 360 kHz. Cabe mencionar que a la salida del comparador se tienen 12 señales (para los Sw pares) y sus complementos (para los Sw impares), dando un total de 24 señales PWM en total.

Los datos de las 24 señales PWM se guardan en una tabla de estados, todos estos elementos establecen los tiempos y los estados de conmutación que sigue cada uno de los DSeP durante un ciclo de línea. Los datos de esta tabla de datos también conocida como Look-Up Table (LUT) se envían y almacenan en un archivo de texto. En la Figura 4 se muestra el diagrama de bloques de las operaciones que se realizan en el script de Matlab.

El uso de una LUT permite ahorrar tiempo de procesamiento, ya que es mucho más rápido recuperar un valor de la memoria que hacer operaciones y cálculos complejos con el FPGA. En este caso, los datos almacenados en la LUT pre-calculada en Matlab determinan las condiciones de operación del inversor. Es posible tener una o más LUT en el mismo programa para efectuar cambios, por ejemplo, modificar el índice de modulación para obtener un voltaje de salida variable. Esto se puede hacer fácilmente, generando una LUT para cada índice de modulación que se pretenda obtener.

b) Programación en Quartus II

El programa principal es un código escrito en lenguaje VHDL utilizando el software Quartus II. La estructura general de este programa consta de tres etapas:

Declaración de librerías, parámetros de entrada/salida, constantes y tipo de señales utilizadas en el programa.

Divisor de frecuencia basado en contadores para generar una señal a una frecuencia determinada (360 kHz), que depende de la frecuencia de la señal moduladora.

Bloque con sentencias secuenciales del tipo case, en el cual se utilizan los datos almacenados en el archivo de texto que genera el script de Matlab para enviar las señales de salida, asignando el tiempo en que cada señal está en un estado alto (encendido) o bajo (apagado).

En la Figura 5 se muestra el esquema que describe la estructura de este programa, generado por el software Quartus II. Este modelo, comúnmente llamado Transferencia Lógica de Registros (RTL, por sus siglas en inglés Register Transfer Logic), describe el programa en términos de cómo los datos se mueven a través de los registros del sistema.

El siguiente paso es comprobar que el código VHDL funciona y ejecuta correctamente las tareas para las que se diseñó. En el archivo de la simulación se utiliza un reloj de 20ns, cuyo periodo corresponde a la frecuencia de 50MHz del reloj interno del FPGA. En la Figura 6 se muestran la señal de referencia a 60Hz y las señales PWM obtenidas mediante simulación en ModelSim.

Después de concluir el proceso de diseño y validación del algoritmo, el archivo generado por el software Quartus II, se utiliza para programar el FPGA. El archivo compilado se transfiere al FPGA a través de una interfaz serie (JTAG) mediante el ByteBlaster de Altera.

c) Simulación del inversor-técnica de modulación

La técnica de modulación se evaluó mediante simulación en PSpice, utilizando el diagrama de conexión que se muestra en la Figura 1. Se realizaron distintas pruebas modificando el índice de modulación para obtener un voltaje de salida variable. Los parámetros empleados se muestran en la Tabla 2.

Tabla 2: Parámetros utilizados en simulación

| Parámetro | Valor |

|---|---|

| Voltaje de entrada (VCD) | 60 V |

| Resistencia de carga (R) | 100 Ω |

| Amplitud de moduladora (Am) | 1.4/1.8 V |

| Frecuencia de moduladora (fm) | 60 Hz |

| Amplitud de portadora (Ap) | 0.5 V |

| Frecuencia de portadora (fp) | 3.6 kHz |

Para la evaluación experimental se utilizaron los módulos IRAM136-1561A (este módulo soporta 600V y puede conducir hasta 15 amperios de forma nominal), cada módulo presenta la configuración típica de un inversor puente completo trifásico y un circuito para acondicionar las señales de activación de los IGBT, con un tiempo muerto entre los interruptores de una misma rama.

d) Plataforma de pruebas

En la Figura 7 se muestra el banco de pruebas experimentales utilizado. La Sección marcada con la letra A corresponde al FPGA, en B se encuentra el inversor multinivel en cascada (para la fase A), en el recuadro marcado con la letra C se encuentran las fuentes de alimentación. Finalmente, en la sección D se encuentra la resistencia de carga y en el recuadro E se encuentra el osciloscopio digital.

Resultados

Para comprobar el correcto funcionamiento de la modulación implementada en el FPGA, se realizaron las pruebas variando el índice de modulación de 0.5 a 1. Sin embargo, con la finalidad de sintetizar los resultados obtenidos y por ser los más comunes solo se presentan dos índices de modulación (0.7 y 0.9). En esta sección se comparan y discuten los resultados obtenidos en simulación y experimentalmente.

1. Simulación

En la Figura 8 se muestra la forma de onda de voltaje obtenida mediante simulación, medida de la fase A al neutro (VAN) con un índice de modulación: a) m=0.7 y b) m=0.9. Se observa, que el voltaje obtenido se incrementa cuando el índice de modulación es mayor. En ambos casos, se obtiene una forma de onda de cinco niveles (+2VCD, +VCD, 0, -VCD y -2VCD).

2. Experimental

En la Figura 9 se muestra la forma de onda de voltaje obtenida experimentalmente, medida de la fase A al neutro (VAN) con un índice de modulación: a) m=0.7 y b) m=0.9. Se puede observar que los resultados obtenidos experimentalmente son muy similares a los que se obtuvieron mediante simulación.

En la Tabla 3 se presenta la comparación de los resultados obtenidos en simulación y de manera experimental. Se puede observar un incremento en el voltaje de salida y una reducción en la THD al aumentar el índice de modulación.

Conclusiones

En este artículo se presenta una metodología para generar de manera digital, las señales PWM de un inversor multinivel utilizando un dispositivo FPGA. El procedimiento empleado para generar estas señales se divide en dos programas; un script de Matlab y un código VHDL creado en el software Quartus II. El proceso de diseño presentado es simple, rápido, flexible y se puede ajustar para implementar otras técnicas de modulación que utilizan múltiples señales portadoras.

La técnica de modulación implementada en el FPGA se verifica en simulación utilizando el programa ModelSim y experimentalmente en un inversor multinivel en cascada trifásico para generar cinco niveles en el voltaje de salida con diferentes índices de modulación.

Los resultados obtenidos experimentalmente se comparan con los conseguidos en simulación con el software PSpice. El análisis de los resultados permite comprobar el correcto funcionamiento de la metodología propuesta para implementar la técnica de modulación en el FPGA. Además, se consigue cambiar el índice de modulación de forma rápida y fácil, al modificar solamente una tabla.

nueva página del texto (beta)

nueva página del texto (beta)