1. Introducción

El diseño de circuitos electrónicos con tecnología CMOS se basa en el uso de transistores MOS como elemento básico, siendo la base de memorias, procesadores, circuitos digitales o analógicos [1]. Aunque la tecnología CMOS es la más utilizada, sus procesos de fabricación a alta temperatura limitan su aplicación en sustratos flexibles de bajo costo, tales como plástico o papel. Esto crea una ventana de interés para el desarrollo de electrónica reciclable, flexible, vestible entre otras, debido a la gran versatilidad que se ha mostrado para fabricar diferentes dispositivos (resistencias, capacitores, diodos o transistores) con diferentes procesos de fabricación y nuevos materiales semiconductores a baja temperatura [2-6]. Para el desarrollo de esta tecnología emergente, una de las claves radica en la fabricación de transistores de película delgada (TFTs) como elemento básico, al igual que los transistores MOS en la tecnología CMOS. Para la fabricación de TFTs se han desarrollado una gran variedad de técnicas de depósito compatibles con diferentes sustratos [7]. Más allá que los TFTs suelen ser conocidos por su principal uso en pantallas de cristal líquido, aun no se conoce el potencial de los circuitos de TFTs en términos de desarrollo para nuevas tecnologías, dado que los circuitos con TFTs se pueden fabricar en sustratos grandes, creando así una electrónica de bajo costo, reciclable y flexible [8,9]. Por lo tanto, es necesario el estudio de diversos materiales como semiconductores, dieléctricos o electrodos para su uso en TFTs sobre plástico.

Una clase de materiales que resulta prometedora para los TFTs sobre plástico son los semiconductores policristalinos y amorfos, debido a su amplio desarrollo en las ultimas décadas. El principal problema de usar semiconductores policristalinos y amorfos es su baja temperatura de depósito, esto resulta en que las propiedades electrónicas se vean afectadas, disminuyendo así el desempeño eléctrico cuando se utilizan en dispositivos semiconductores. Por lo tanto, es de gran interés el depósito de películas amorfas o policristalinas con excelentes propiedades electrónicas cuyo desempeño no dependa del grado de desorden atómico [10]. En este aspecto, dentro de los materiales más recientes, los óxidos semiconductores destacan debido a que exhiben una combinación de características tales como alta transparencia óptica y alta movilidad de portadores sin importar su estructura policristalina o amorfa, las cuales representan una nueva ventana para diferentes aplicaciones [11]. El óxido de zinc (ZnO) es un oxido semiconductor que posee una alta movilidad de electrones, alta conductividad térmica y un gran ancho de banda prohibida que lo hacen adecuado para una amplia gama de dispositivos, incluidos transistores de película delgada transparentes [12]. Además, existe una gran variedad de técnicas de depósito tales como sputtering, deposito químico en fase vapor (CVD) o alguna de sus variantes, sol-gel, spin coating o spray pyrolysis [13-15]. Dentro de las opciones de las técnicas de depósito por solución, la técnica de spray pyrolysis ultrasónico, es una técnica de depósito muy versátil, sencilla y de muy bajo costo para obtener películas de ZnO [16]. La importancia de esta técnica recae en la uniformidad y compatibilidad con sustratos de área grande para el depósito de películas delgadas [17-20]. Por lo tanto, los dispositivos fabricados en sustratos flexibles tendrían muchas aplicaciones novedosas, como pantallas flexibles, etiquetas de identificación por radiofrecuencia (RFID), celdas solares, “piel” electrónica, sensores de presión, sensores de temperatura, sensores químicos y biosensores [21-23].

En este trabajo, se presenta la fabricación y caracterización de ZnO TFTs en sustratos de plástico. Las películas delgadas se depositaron mediante un sistema de depósito de spray pyrolysis ultrasónico de alta frecuencia hecho en casa. El tereftalato de polietileno (PET) se usa como sustrato plástico. El ZnO y aluminio se usaron como película semiconductora y electrodo, respectivamente. Se usó spin-on glass (SOG) como película dieléctrica. La temperatura máxima del proceso fue de 200◦C. Además, capacitores metal-dieléctrico-metal (MIM) fueron fabricados sobre plástico y caracterizados para evaluar el desempeño del dieléctrico de compuerta.

2. Experimental

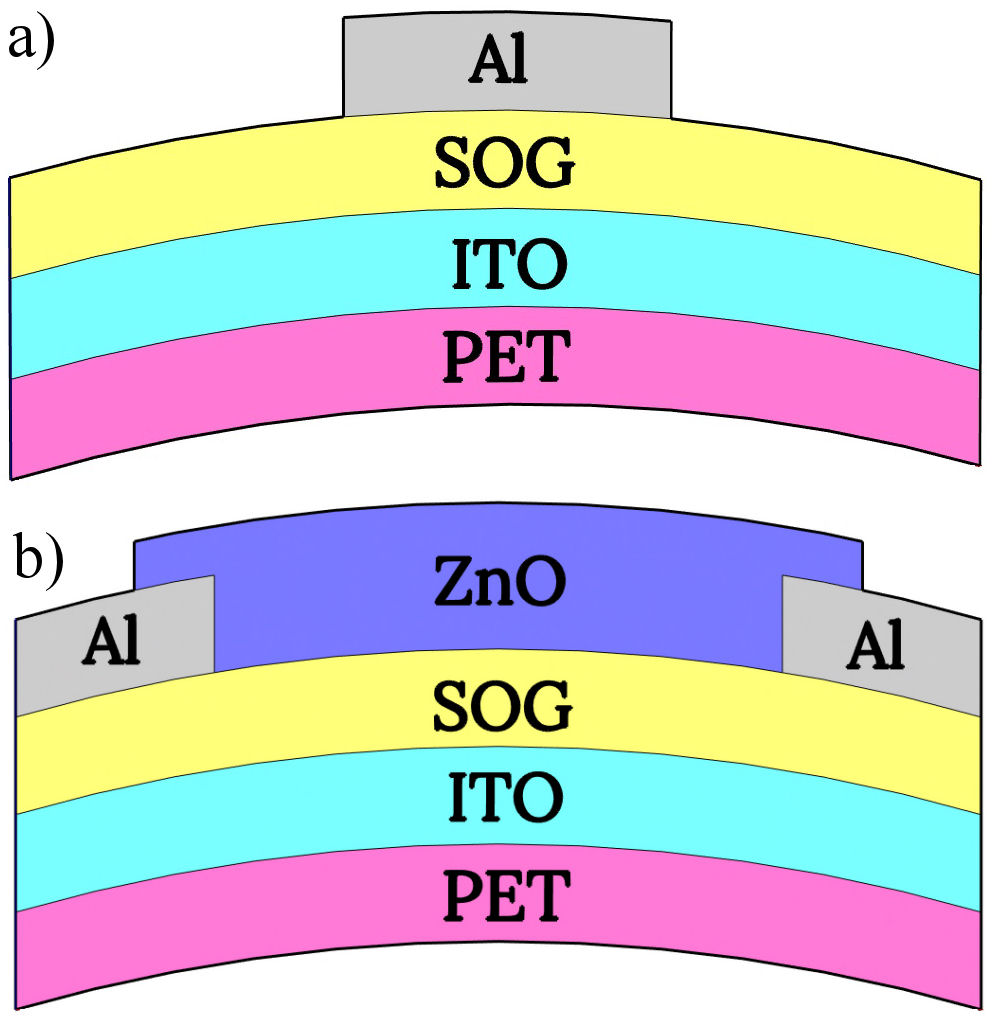

Se fabricaron dos dispositivos, a saber, capacitores MIM y TFTs, como se muestra en la Fig. 1. Como sustrato para los dispositivos se utilizó PET recubierto con ITO disponible comercialmente por Sigma-Aldrich. Como película dieléctrica se utilizó SOG, la solución precursora fue preparada con un 33% de LSF47-SOG en 66% del solvente LSFD1 (Filmtronics), depositado por spin coating a 3000 RPM por 30 segundos con un recocido de 10 minutos a 100◦C y un tratamiento térmico a 200 ◦C por 2 horas. Para la obtención de ZnO, la solución precursora de 0.2M de acetato de zinc (99.99% sigma-aldrich) diluido en metanol, fue depositada a 200◦C por 10 min, por el sistema de spray pirolisis ultrasónico de alta frecuencia hecho en casa. Este sistema se adaptó de un nebulizador comercial Citizen (Cun60), con un transductor ultrasónico que opera a 2.5 MHz. La película de ZnO tuvo un grosor de ∼ 100 nm que se midió con un perfilometro (DEKTAK 150). Los contactos de drenaje y fuente fueron de aluminio evaporado por medio de una pistola de electrones, fotolitograbados y formados por grabado húmedo. Los contactos de aluminio tuvieron un grosor de 100 nm. La Fig. 1a) muestra el esquema de la estructura fabricada de los capacitores MIM, donde primero se depositó el SOG en el sustrato de PET con ITO, seguido de los contactos de aluminio teniendo una estructura ITO/SOG/Al. La Fig. 1b), muestra el esquema de la estructura fabricada de los ZnO TFTs con una estructura coplanar invertida, primero se depositó SOG en el sustrato de PET con ITO, seguido de los contactos de aluminio y por último se depositó la película de ZnO, como se muestra en la Fig. 2. La caracterización eléctrica se realizó mediante el sistema de caracterización de semiconductores Keithley-4200, en condiciones de oscuridad y temperatura ambiente.

FIGURE 1 a). Representación esquemática de la sección transversal del capacitor MIM, con estructura PET/ITO/SOG/Al. b) Representación esquemática de la sección transversal de la estructura coplanar invertida (PET/ITO/SOG/Al/ZnO) usada en los ZnO TFTs sobre sustratos de plástico PET.

3. Resultados y discusión

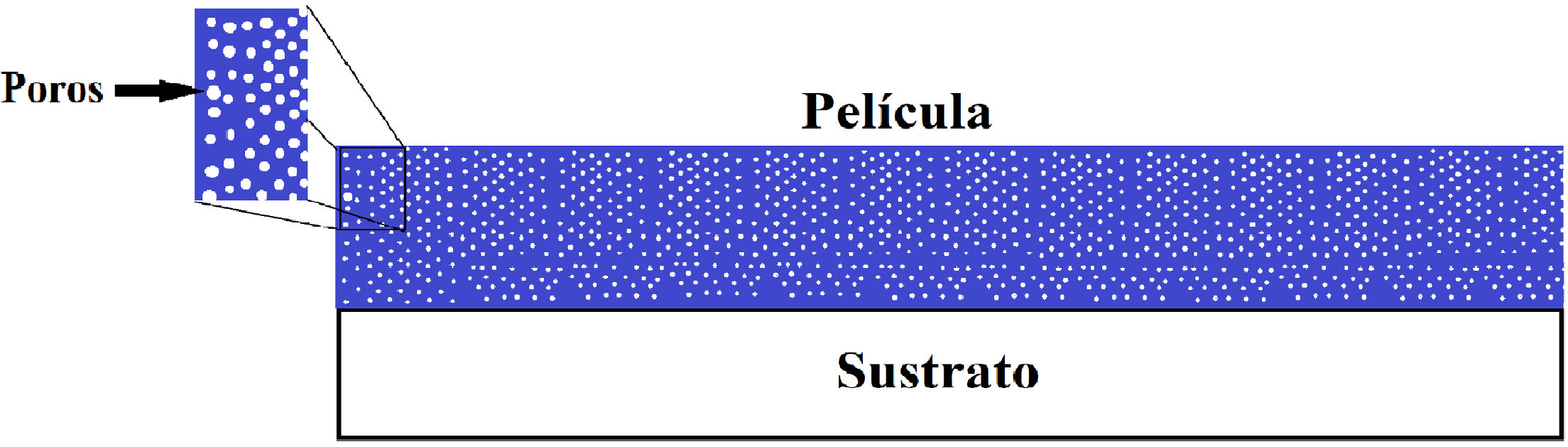

Una de las técnicas más utilizadas en la microelectrónica es spin coating debido a su uso en foto-resinas y depósito de películas delgadas [24]. La Fig. 3 muestra el esquema del sistema de spin coating, el cual consiste en aplicar la solución precursora a la muestra, que esta sobre un porta-sustrato, el´ cual gira para el esparcimiento de la solución. Una vez que se obtiene una solución uniforme sobre la muestra, se aplica un tratamiento térmico para la evaporación de los solventes y obtener una película delgada [25]. Como se da un tratamiento térmico, la evaporación de los solventes de la solución pre-cursora van generando poros en la película delgada, resultando en una película con baja densidad como se muestra en la Fig. 4 [26].

FIGURE 3 Esquemático del proceso de depósito por el método de spin-coating. Debido a los poros generados durante la evaporación de los solventes, la película delgada obtenida tiene una baja densidad.

FIGURE 4 Película delgada porosa después del tratamiento térmico debido a la evaporación de los solventes de la solución precursora por spin coating.

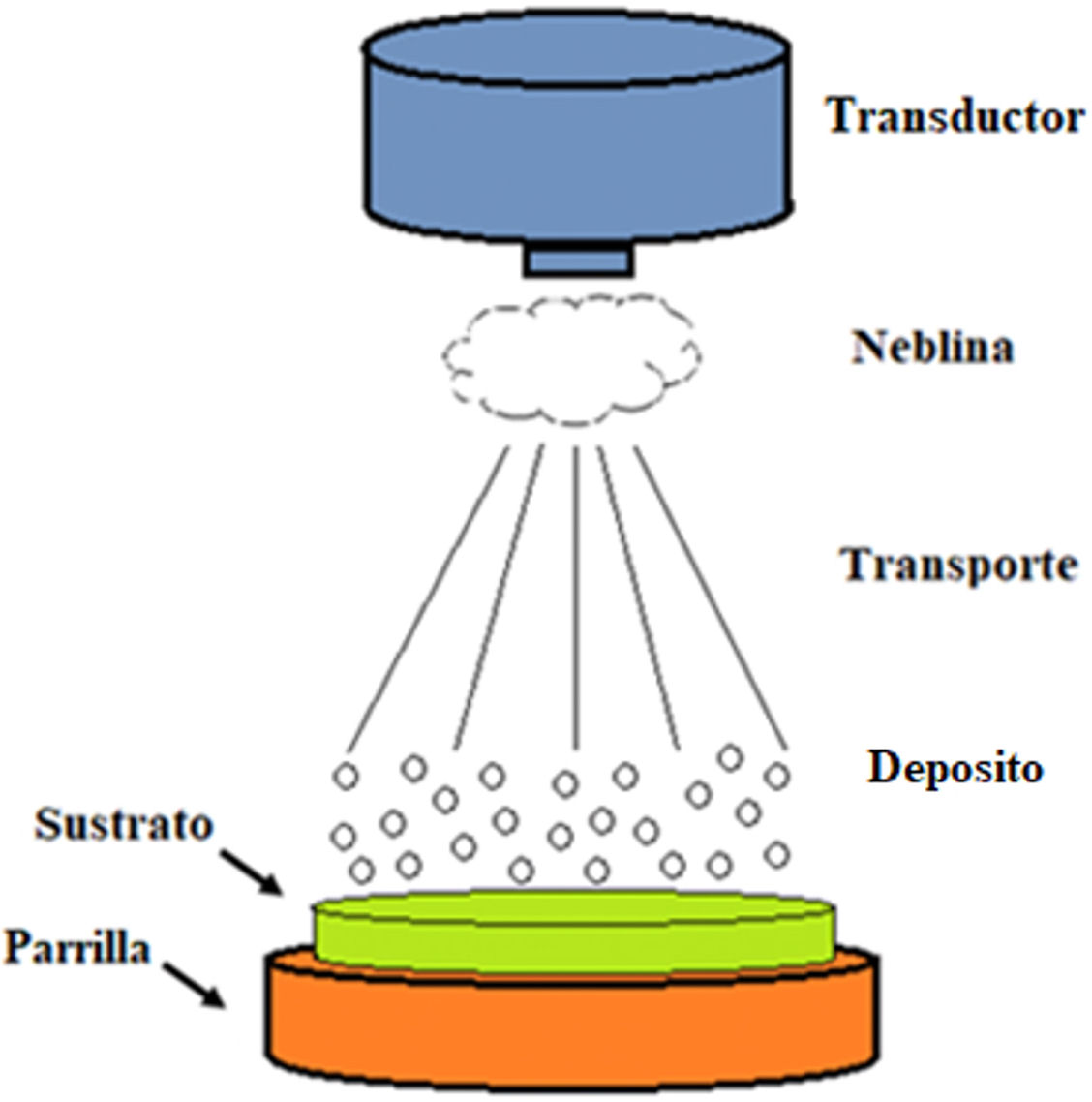

En la Fig. 5 se muestra el sistema de spray pyrolysis ultrasónico, el cual consiste en un transductor ultrasónico que genera una neblina de la solución precursora, esta es arrastrada usando aire hasta llegar a la muestra. Mientras la muestra se encuentra sobre una parrilla caliente (a la temperatura de depósito), la solución precursora llega a la superficie, evaporando los solventes mientras se realiza la descomposición química para ir depositando la película delgada. Durante el proceso de depósito se generan poros, por la evaporación de los solventes, pero estos son llenados por nueva solución nebulizada, creando una película más densa y homogénea en comparación con las películas obtenidas por spin-coating [27-37]. Una frecuencia más alta en el transductor genera una neblina más fina que permite depositar películas aún más densas [37]. Desafortunadamente, la mayoría de los trabajos reportados con spray pyrolysis ultrasónico no mencionan la frecuencia de operación del transductor, mientras que los trabajos que lo hacen reportan una frecuencia del orden de los kHz [27-39].

FIGURE 5 Esquemático del proceso de depósito de spray pyrolysis. Este método consiste en un transductor que genera una neblina por medio de vibraciones ultrasónicas, la cual es arrastrada por un gas (aire) hasta el sustrato mientras se encuentra sobre una superficie caliente.

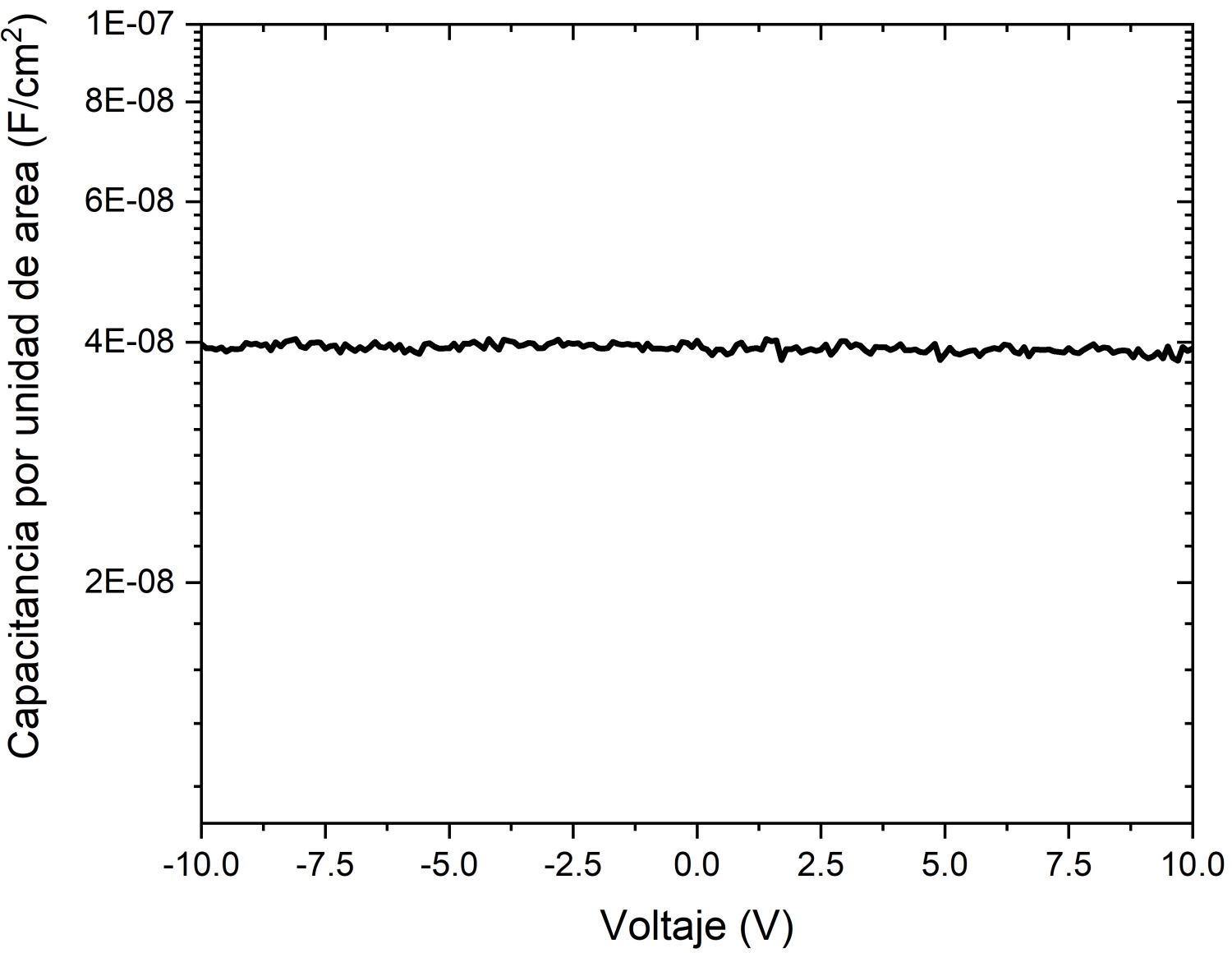

En la Fig. 6 se muestra la curva capacitancia-voltaje (CV) de los capacitores MIM, donde la capacitancia por unidad de área es ∼ 4×10−8 F/cm2, que es constante en voltajes de −10 a 10 V. Se considera que el comportamiento del capacitor MIM se relaciona con la existencia de atrapamiento de carga en el dieléctrico. Diferentes trampas inducirán cargas con diferentes constantes de tiempo y modularan fuertemente a las cargas de los capacitores [40].

FIGURE 6 Curva característica C-V del capacitor MIM, donde la capacitancia por unidad de área es constante a altos voltajes y con diferente polarización. Demostrando el uso del SOG como dieléctrico de compuerta.

En la Fig. 7 se muestra la curva de corriente-voltaje (IV) de los capacitores MIM con un barrido de ±15 V, donde se puede apreciar el valor de la corriente de fuga ∼ 10−5 A/cm2. Este comportamiento es superior a lo reportado en la literatura con diferentes dieléctricos [41-44]. Chakraborty et al. [42] obtienen películas de ZrO2 por la técnica de PECVD con corrientes de fuga de 10−1 a 10−2 A/cm2 a 3 V como dieléctrico de compuerta. Qiang Lu et al. [43] reportan películas ultradelgadas de Ta2O5 por CVD sobre sustratos de silicio con corrientes de fuga de 10−5 A/cm2 a 3 V.

FIGURE 7 Curva característica I-V de la estructura MIM para determinar la corriente de fuga del dieléctrico.

Estos valores bajos de corriente de fuga no causaran una pérdida de señal en circuitos electrónicos, además que evitaran un gran consumo de energía [45]. Esto ayuda a la búsqueda de un dieléctrico de compuerta con excelentes parámetros tanto en densidad de carga como en la corriente de fuga [46]. De acuerdo con la Figs. 6 y 7, los capacitores fabricados con spin coating presentan buenas características con propiedades aproximadamente iguales a las reportadas del SiO2 crecido térmicamente [47-49]. Además, se puede establecer una relación de los capacitores MIM y el dieléctrico del TFT, ya que la calidad de este puede reducir la corriente de fuga, no afectar la transconductancia del TFT e incrementar la corriente de drenaje I D .

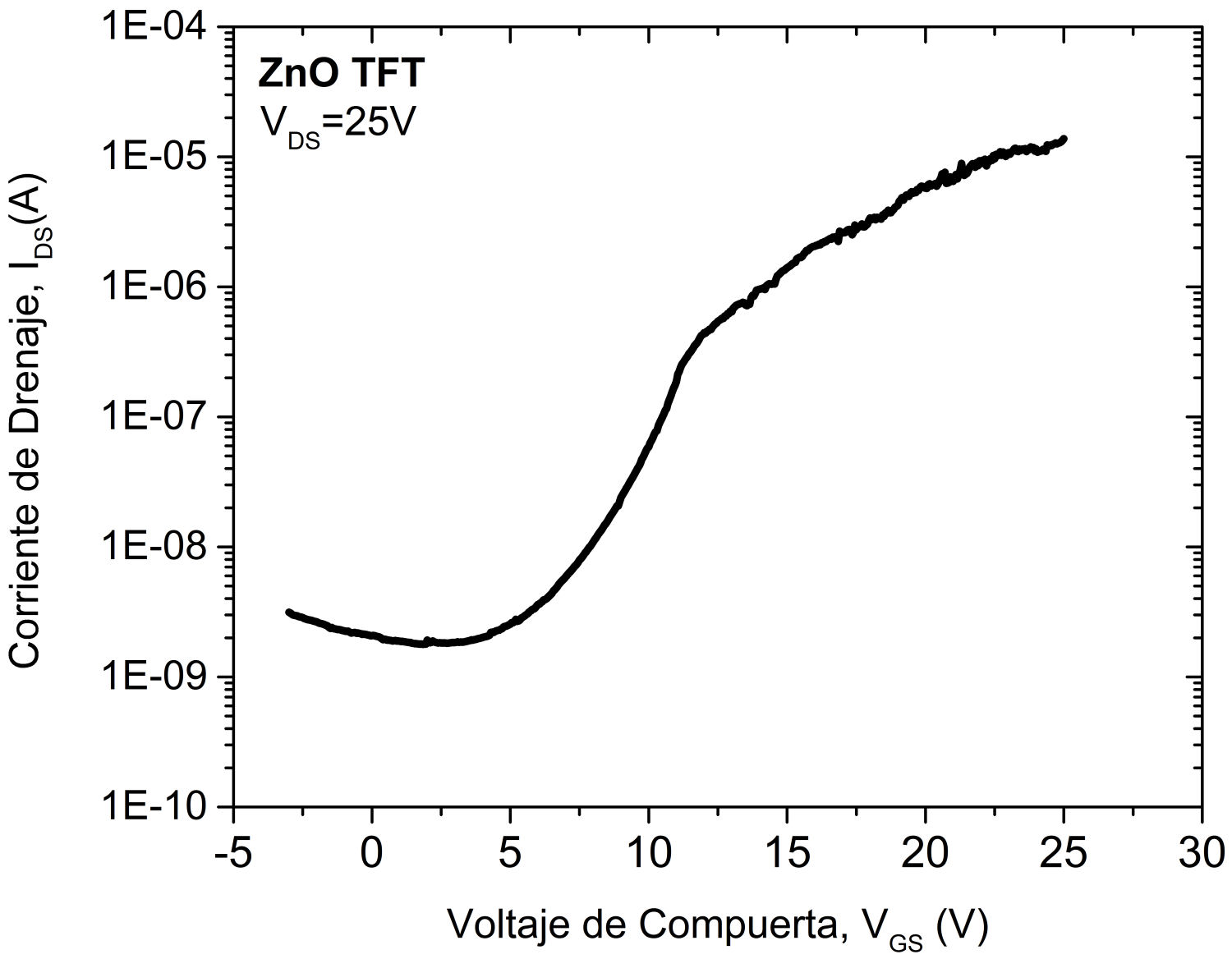

En la Fig. 8 se muestra la curva de transferencia de los ZnO TFTs. El TFT trabaja en modo de enriquecimiento, es decir, la corriente de drenaje (I D ) incrementa con el voltaje de compuerta (V GS ). A partir de la curva de transferencia, se puede estimar las principales figuras de mérito como el voltaje de umbral la pendiente de subumbral (S), la movilidad de efecto de campo µ FE , la relación de encendido/apagado ION/OFF [50]. La pendiente de subumbral S, está definida por la variación del voltaje de compuerta que necesita para producir un cambio de 1 década en la corriente I D , donde se utiliza la siguiente ecuación [51]:´

FIGURE 8 Características de transferencia de los ZnO TFTs mostrando el comportamiento típico reportado. Se muestra una relación de corriente encendido/apagado de 104 y un voltaje de umbral de 10.5 V.

Obteniéndose un valor de 2.71 V/DEC para los ZnO TFTs. A su vez la pendiente de subumbral depende de la densidad de trampas en el ZnO (N T ) y de la densidad de trampas en la interface (D it ) entre el ZnO y el SOG. Por lo tanto, la pendiente de subumbral puede ser aproximada como:

donde q, k B , T, t s , y C i son la carga del electrón, la constante de Boltzmann, la temperatura absoluta, el grosor del semiconductor y la capacitancia por unidad de área del dieléctrico, respectivamente [45]. Si N T o D it se asumen por separado como cero, se pueden obtener los valores máximos de cada uno. Los valores obtenidos son N T = 1.33×1017 cm−3eV−1 y D it = 1.1305 × 1013 cm−2eV−1, que son similares a los reportados en TFTs con ZnO [52,53].

La relación I ON/OFF es una importante figura de mérito, donde la corriente de apagado debe ser lo más baja posible para lograr una alta relación con la corriente de encendido y minimizar el consumo de energía en el estado apagado [54]. En nuestros ZnO TFTs, la relación I ON/OFF es 104 y es comparable con otros trabajos reportados [55-57]. Jin Hyung et al. [55] reportan valores de I ON/OFF de 103 en TFTs de ZnO por procesos por solución, con una temperatura menor a 200◦Cy sobre sustratos PET. Chen Sha et al. [56] reporta valores de I ON/OFF de 105 en TFTs depositados por spin coating sobre vidrio.

En la Fig. 9 se muestra la relación (I DS ) 1/2 vs V GS con la cual se obtienen los parámetros eléctricos característicos de los TFTs como, el voltaje de umbral (V T ) que se define como el voltaje de compuerta al cual los electrones de conducción empiezan a aparecer en el canal [58]. El valor de V T se puede obtener por la extrapolación en la región lineal, siendo quizás el método de extracción de voltaje umbral más popular. Este consiste en encontrar la intersección del eje del voltaje de compuerta de la extrapolación lineal de la curva (I D ) 1/2 vs V G en su punto máximo de la derivada (pendiente) [58,59]. Obteniendo la intersección del eje de voltaje de compuerta se encuentra un valor de 10.5 V.

FIGURE 9 Ajuste de normalización (I DS ) 1/2 de la curva de transferencia de los ZnO TFTs utilizado para la extracción de la movilidad de efecto de campo y el voltaje de umbral en régimen de saturación.

Por otro lado, la movilidad efecto de campo fue obtenida usando la Ec. (3), en el régimen de saturación del TFT,

donde µ FE es la movilidad de efecto de campo, C OX es la capacitancia por unidad de área del dieléctrico de compuerta (4×10−8 F/cm2), V T es el voltaje de umbral, W y L es el largo y ancho del canal, respectivamente [59,60]. La movilidad obtenida fue de 1.25 cm2/Vs. Otros reportes en la literatura de ZnO TFTs hacen mención de valores de movilidad que están entre 1-15 cm 2/Vs para diferentes TFTs de óxidos semiconductores a temperaturas de 100-600◦C. [60-65]. Vidor et al. [64] reportan movilidades de electrón desde 0.5 cm 2/Vs para TFTs con nanopartículas de ZnO sobre sustratos flexibles con spray pyrolysis convencional. Ming-Dong et al. [65] reporta movilidades de electrón de 0.6 cm 2/Vs con TFTs de ZnO por spray pyrolysis con temperatura de fabricación de 400◦C.

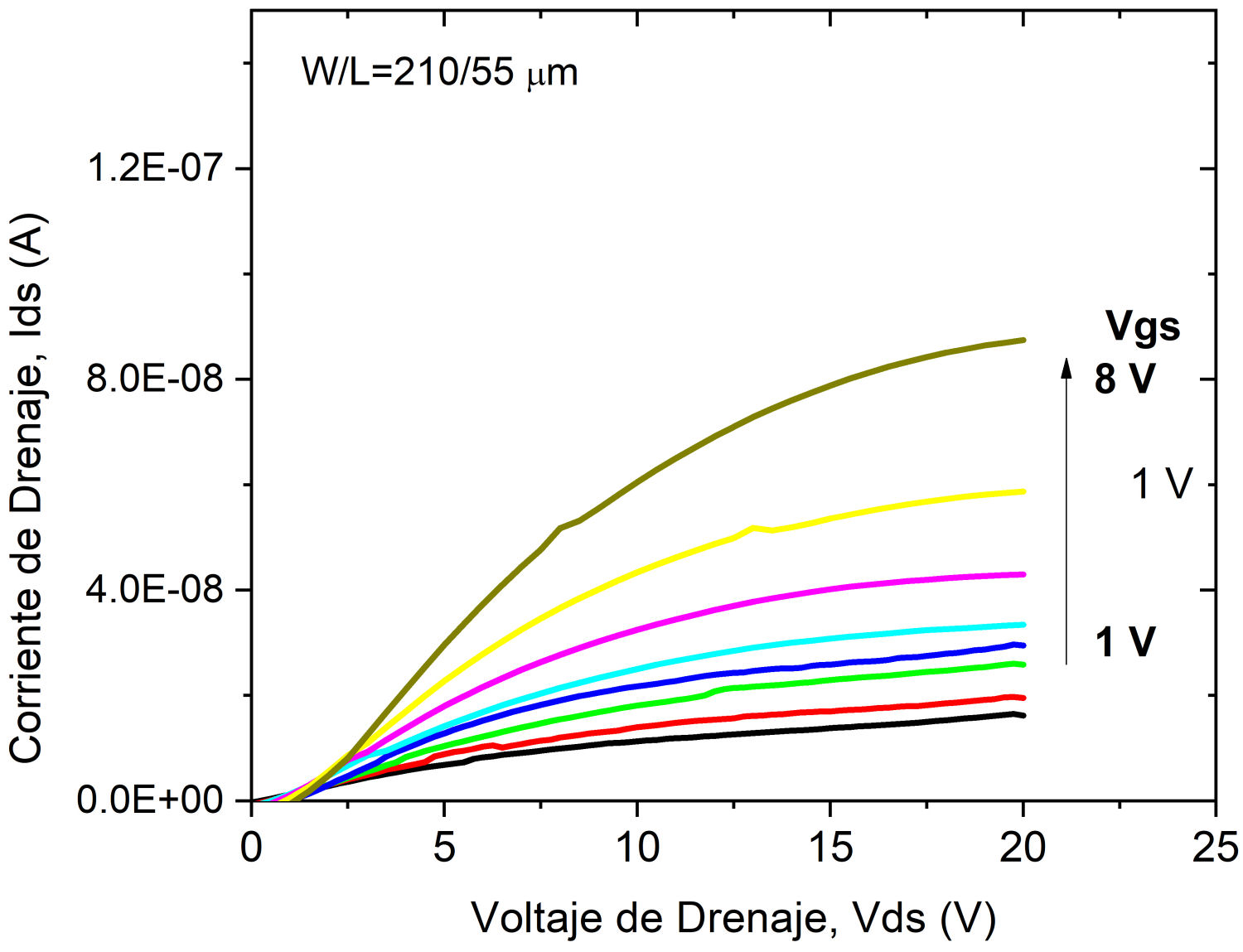

En la Fig. 10, se muestran las características de salida de los ZnO TFTs sobre sustratos de plástico. La familia de curvas de salida es la corriente de drenaje (I D ) en función de un barrido de voltaje de drenaje (V DS ) y a diferentes voltajes de compuerta (V GS ).

FIGURE 10 Características de salida de los ZnO TFTs. Se muestra una modulación en la corriente Ids en función del voltaje de compuerta V gs .

Cuando se aplican valores bajos de voltaje de V DS , la concentración de portadores en el canal es menor y la corriente I DS incrementa linealmente (régimen lineal). A altos voltajes de V DS la concentración de portadores se incrementa y la corriente es mayor (régimen de saturación). El TFT entra en el régimen de saturación cuando V DS > V SAT , donde V SAT = V GS − V T [66]. Los ZnO TFTs claramente exhiben el régimen lineal y de saturación, mientras la corriente de drenaje es modulada con el voltaje de compuerta V GS .

Sin embargo, la familia de curvas de salida exhibe un efecto conocido como “current crowding” a valores de V DS < 2 V, donde la distribución de la densidad de corriente se vuelve no ohmica a través del área de contacto, y se sabe que podría conducir a fallas del dispositivo a través de la formación de puntos térmicos y de electromigración [67]. También proporciona una característica cualitativa de la resistencia de contacto, un parámetro importante independiente´ del área útil para comparar diferentes contactos [68,69]. Los resultados de la Fig. 10 sugieren una alta resistencia de contacto, como resultado de una posible capa de Al2O3 formada en la interfaz metal-semiconductor (Al/ZnO) durante la fabricación de los dispositivos [70]. Se ha demostrado que al dar tratamientos térmicos a bajas temperaturas se pueden mejorar´ las características eléctricas de los dispositivos sin deformar el sustrato de plástico [71]. En la Tabla I se hace un resumen de las características de los ZnO TFTs en este trabajo con otros reportados en la literatura.

4. Conclusión

En resumen, se comprueba la calidad del dieléctrico (SOG) por medio de capacitores MIM procesados por solución, obteniendo una baja corriente de fuga (∼ 10−5 A/cm2) a voltajes de 15 V, esto se asemeja a valores de SiO2 crecidos térmicamente. Además, los ZnO TFTs depositados por el método de spray pyrolysis ultrasónico a alta frecuencia, presentan´ parámetros prometedores como la movilidad de portador cercana a 1.25 cm2/Vs, aproximadamente como se reporta en la literatura para ZnO TFTs. También, el voltaje de umbral con valor de 10.5 V y la relación de encendido/apagado (I on/off) de 104 son similares a lo reportado en la literatura. Asimismo, se corroboro que a pesar de la baja temperatura de fabricación y no requerir vacío, el aumento de frecuencia a 2.5 MHz es un complemento para obtener una mejor calidad de las películas, debido a que existe una relación entre el tamaño de gota y la homogeneidad de la película con la frecuencia.

nueva página del texto (beta)

nueva página del texto (beta)